#### REPUBLIQUE ALGERIENNE DEMOCRATIQUE ET POPULAIRE MINISTERE DE L'ENSEIGNEMENT SUPERIEUR ET DE LA RECHERCHE SCIENTIFIQUE

UNIVERSITE FRERES MENTOURI CONSTANTINE I FACULTE DES SCIENCES EXACTES DEPARTEMENT DE PHYSIQUE

N° d'ordre : Série :

# **THÈSE**

# Présentée pour l'obtention du diplôme de DOCTEUR EN SCIENCES EN PHYSIQUE

SPECIALITE : ENERGÉTIQUE OPTION : PHOTOVOLTAIQUE

#### **THÈME**

# ÉTUDE DES PROPRIÉTÉS STATIQUES ET DYNAMIQUES DU TRANSISTOR À GRILLE ISOLÉE MOSFET

#### PAR:

#### BENZAOUI OUASSILA

Devant le jury composé de :

Président: S. BENATALLAH M.C.A Univ. Frère Mentouri Constantine I

Rapporteur: C. AZIZI Prof. Univ. Larbi Ben M'hidi Oum El-Bouaghi

Examinateurs: Y. SAIDI Prof. Univ. Frère Mentouri Constantine I

M. ZAABAT Prof. Univ. Larbi Ben M'hidi Oum El-Bouaghi

M. DRAIDI M.C.A Univ. Larbi Ben M'hidi Oum El-Bouaghi

### **Remerciements**

Je tiens tout d'abord à remercier DIEU le tout puissant et miséricordieux, qui m'a donné la force, la volonté, la santé et la patience durant toutes ces longues années d'études afin que je puisse arriver à ce stade.

Mes remerciements vont en particulier à Madame C. AZIZI, professeur à l'université Larbi Ben M'Hidi d'Oum El Bouaghi pour avoir accepté de m'encadrer ainsi que pour ses précieux conseils, ses compétences scientifiques et pour la liberté de recherche qu'elle a bien voulu me laisser.

Je remercie vivement Madame S. BENATALLAH, maitre de conférences A à l'université Frères Mentouri-Constantine I pour l'honneur qu'il m'a fait en acceptant de présider le jury de cette thèse.

Mes remerciements vont également à Madame Y. SAIDI, professeur à l'université Frères Mentouri-Constantine I d'avoir accepté d'être membre de jury.

Mes remerciements vont également à Monsieur M. ZAABAT, professeur à l'université Larbi Ben M'Hidi d'Oum El Bouaghi d'avoir accepté d'être membre de jury.

Mes remerciements vont également à Monsieur M. DRAIDI, maître de conférences A à l'université Larbi Ben M'Hidi d'Oum El Bouaghi d'avoir accepté d'être membre de jury.

Je tiens à remercier très vivement Monsieur F. MORANCHO, Professeur à l'Université Toulouse 3, LAAS/CNRS - Groupe ISGE – France pour son aide, son esprit scientifique et ses qualités humaines.

Enfin, je tiens également à remercier toutes les personnes qui ont participé de près ou de loin à la réalisation de ce travail.

# **DEDICACE**

# Je dédie ce modeste travail

A la mémoire de ma tante

A la mémoire de mon père

A ma chère mère

A mon mari

A mes filles

A mes frères et mes sœurs

A toute ma famille

A tous mes amis

# Sommaire

| Introduction générale                                               | 1  |

|---------------------------------------------------------------------|----|

| Chapitre I : Caractéristiques générales du MOSFET                   |    |

| I.1 Introduction                                                    | 4  |

| I.2 Etat de l'art des transistors                                   | 4  |

| I.2.1 Transistors bipolaires                                        | 6  |

| I.2.2 Transistors unipolaires (transistor à effet de champ)         | 7  |

| I.2.3 Autres transistors                                            | 9  |

| I.3 Présentation du transistor MOSFET                               | 9  |

| I.3.1 DMOSFET                                                       | 11 |

| I.3.2 EMOSFET                                                       | 11 |

| I.4 Généralités sur la structure MOS                                | 12 |

| I.4.1 Diagramme d'énergie d'une structure Métal-Vide-Semiconducteur | 12 |

| I.4.2 Diagramme d'énergie d'une structure MOS                       | 14 |

| I.4.3 Effet d'une polarisation du matériau de grille                | 16 |

| I.5 Principe de fonctionnement d'un MOSFET                          | 17 |

| I.6 Le Silicium                                                     | 20 |

| I.6.1 Structure cristalline                                         | 20 |

| I.6.2 Bande d'énergie interdite                                     | 22 |

| I.6.3 Propriétés physiques et électriques du silicium               | 24 |

| I.6.4 Phénomènes de transport                                       | 24 |

| I.6.4.1 Transport stationnaire                                      | 24 |

| I.6.4.2 Transport non stationnaire                                  | 27 |

| I.7 L'Oxyde de Silicium SiO2                                        | 29 |

| Chapitre II: Propriétés statiques du MOSFET                         |    |

| II.1 Introduction                                                   | 31 |

| II.2 Tension de seuil                                               | 31 |

| II.3 Courant de drain                                               | 33 |

| I.3.1Régime linéaire                                                | 36 |

| I.3.2 Régime saturé                                                 | 37 |

| II.4 Transconductance g <sub>m</sub> et conductance g <sub>d</sub> | 37 |

|--------------------------------------------------------------------|----|

| II.4.1 Transconductance g <sub>m</sub>                             | 38 |

| II.4.2 Conductance g <sub>d</sub>                                  | 39 |

| II.5 Effet des résistances parasites                               | 39 |

| II.6 Effet de la mobilité                                          | 41 |

| II.7 Effet de la température                                       | 43 |

| II.7.1 Paramètres thermiques                                       | 43 |

| II.7.2 Dissipation thermique                                       | 45 |

| Chapitre III : Propriétés dynamiques du MOSFET                     |    |

| III.1 Introduction                                                 | 46 |

| III.2 Schéma équivalent électrique du transistor MOSFET            | 46 |

| III.2.1 Eléments intrinsèques                                      | 47 |

| III.2.1.1 Transconductance g <sub>m</sub> intrinsèques             | 47 |

| III.2.1.2 Conductance gd                                           | 47 |

| III.2.1.3 Capacités grille-source / grille-drain                   |    |

| III.2.1.4 Capacité drain-source                                    | 49 |

| III.2.2 Eléments extrinsèques                                      | 49 |

| III.2.2.1 Résistances                                              | 49 |

| III.2.2.2 Capacités et inductances                                 | 49 |

| III.3 Paramètres dynamiques                                        | 50 |

| III.3.1 Paramètres S parasites                                     | 50 |

| III.3.2 Fréquence de transition $f_t$                              | 52 |

| III.3.3 Fréquence maximale d'oscillation f <sub>max</sub>          | 54 |

| III.3.4 Facteur de stabilité du transistor                         | 55 |

| III.4 Bruit dans les transistors MOSFET                            | 56 |

| III.4.1 Bruit en 1/f ou bruit basse fréquence                      | 56 |

| III.4.1.1 Fluctuations du nombre de porteurs de charge             | 57 |

| III.4.1.2 Fluctuation de la mobilité                               | 58 |

| III.4.2 Le bruit thermique                                         | 58 |

| Chapitre IV : Résultats et interprétations                         |    |

| IV.1 Introduction                                                  | 59 |

| IV.2 Caractéristiques statiques                                    |    |

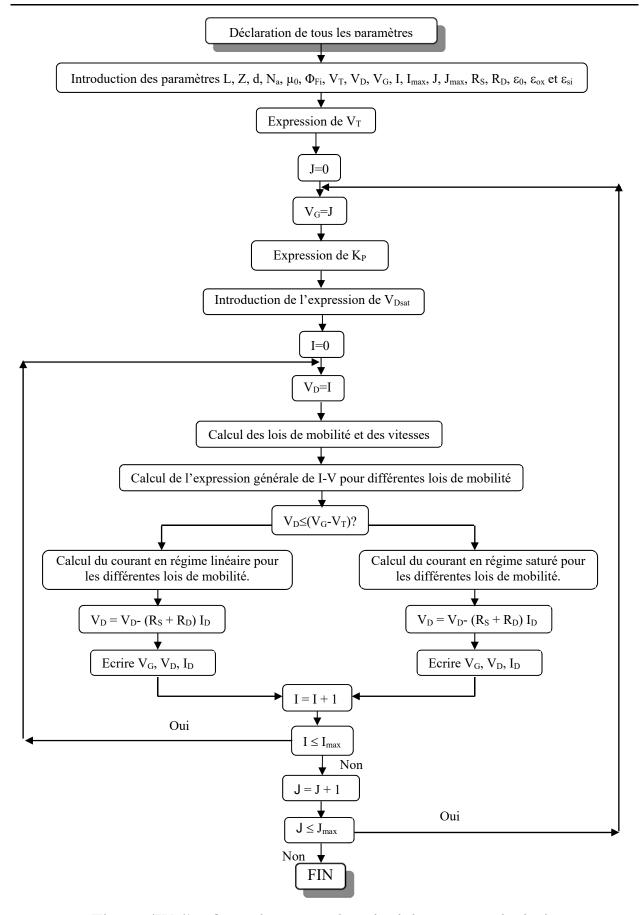

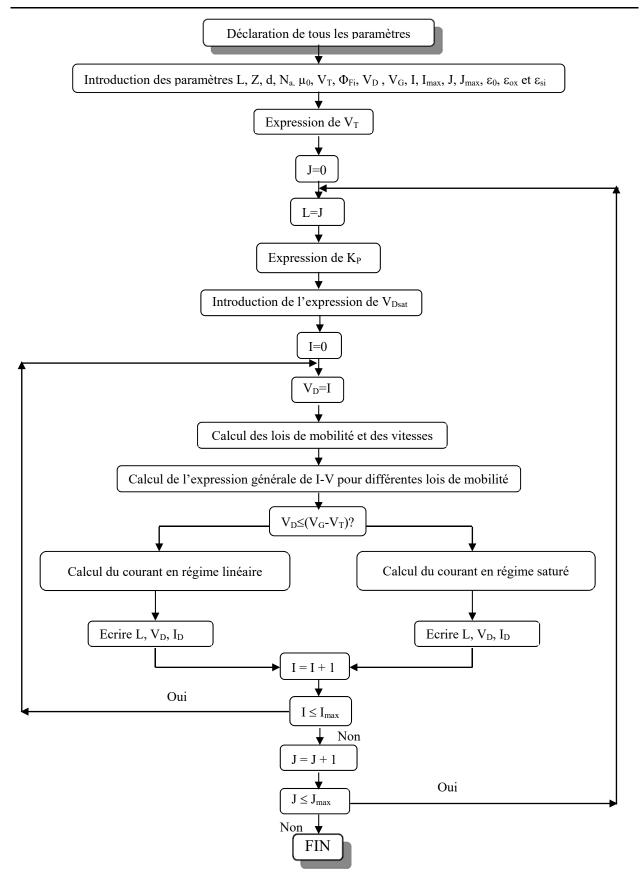

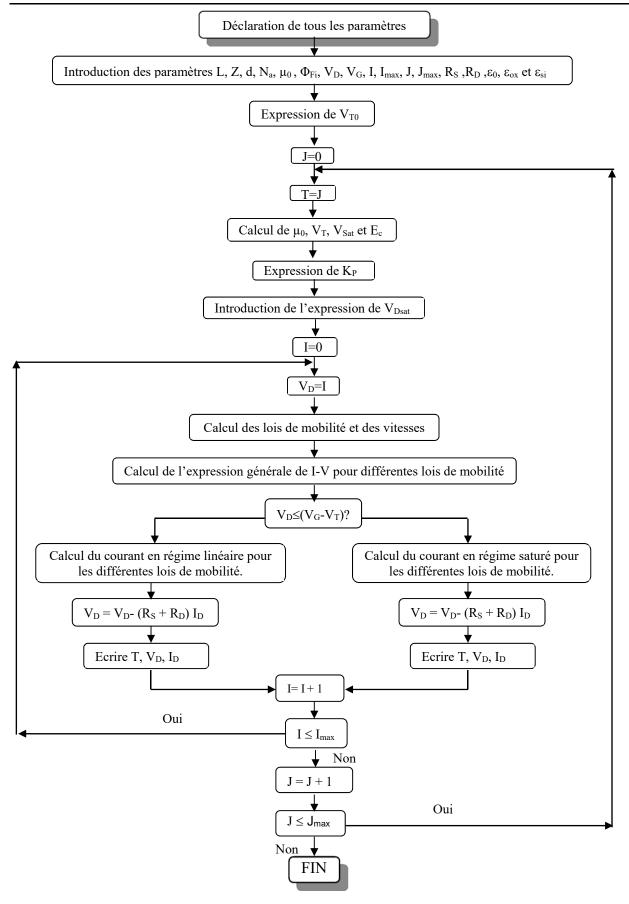

| IV 2.1 logiciel de simulation                                      | 50 |

| Références hibliographiques                              | 9.8 |

|----------------------------------------------------------|-----|

| Conclusion générale                                      | 96  |

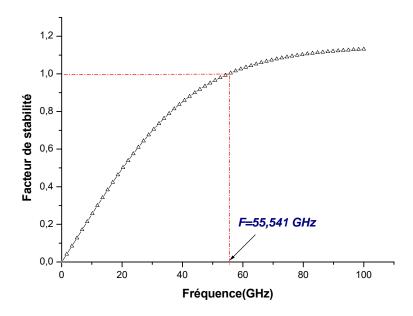

| IV.3.6 Facteur de stabilité k                            | 94  |

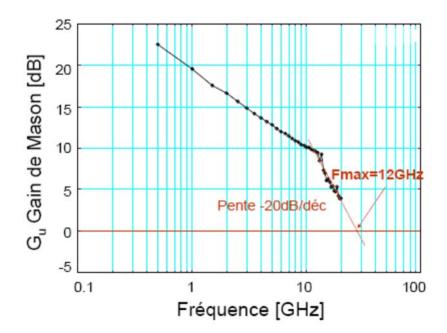

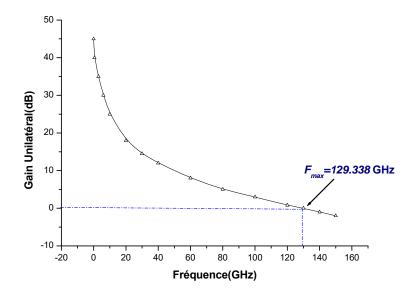

| IV.3.5 Fréquence d'oscillation maximale $f_{max}$        | 93  |

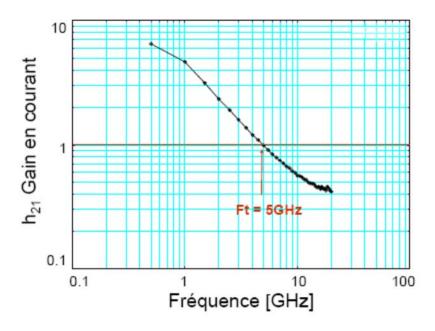

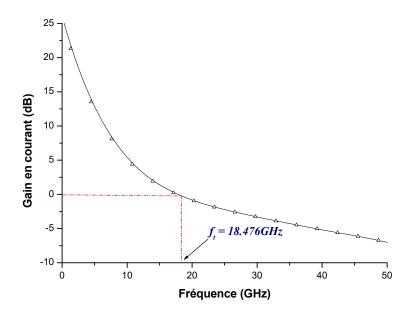

| IV.3.4 Fréquence de transition $f_T$                     | 92  |

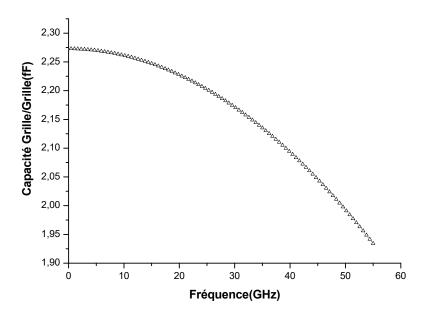

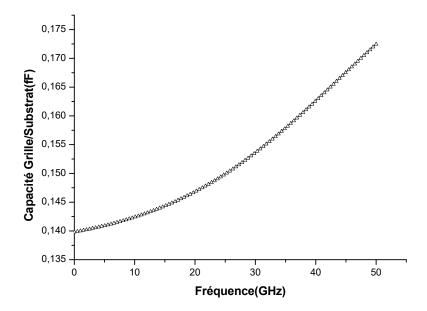

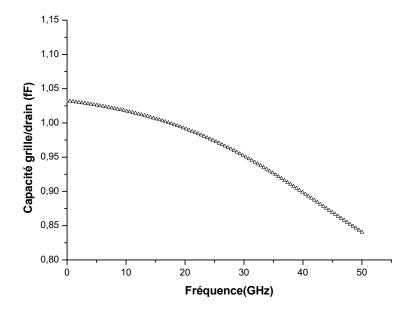

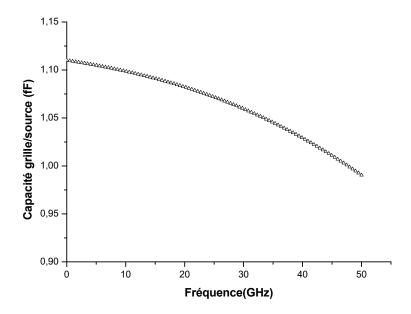

| IV.3.3 Capacités                                         | 90  |

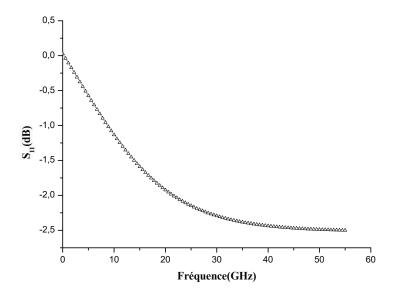

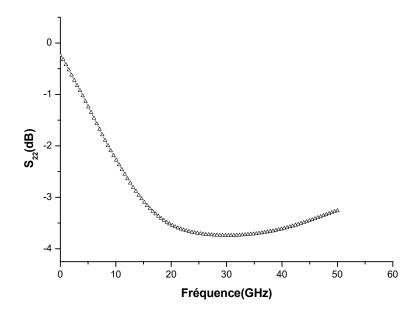

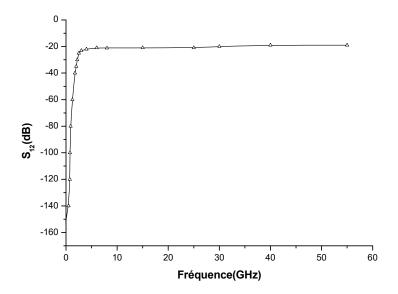

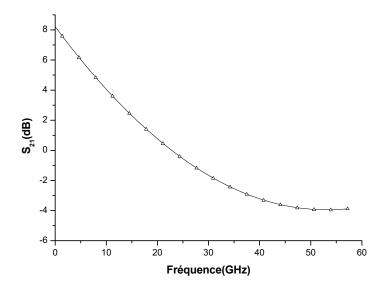

| IV.3.2 Paramètres S                                      | 87  |

| IV.3.1.2.4 Maximum raffinement Per Pass                  | 85  |

| IV.3.1.2.3 Fréquence adaptative                          | 85  |

| IV.3.1.2.2 Nombre maximum d'itération ou nombre de passe | 85  |

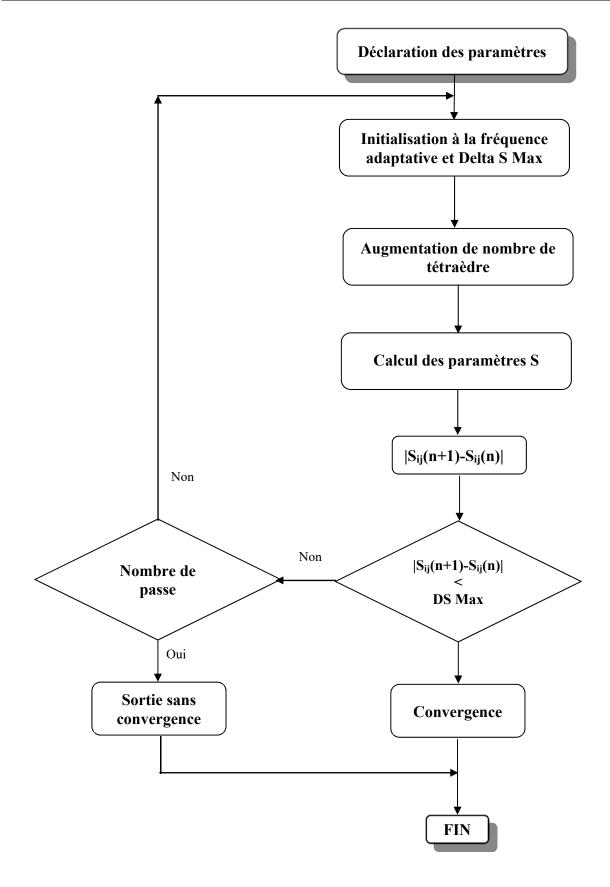

| IV.3.1.2.1 Maximum Delta S et convergence                | 85  |

| IV.3.1.2 Paramètres de maillage du simulateurHFSS        | 84  |

| IV.3.1.1 Méthode des Eléments Finis (MEF)                | 84  |

| IV.3.1 Logiciel de simulation HFSS                       | 84  |

| IV.3 Caractéristiques dynamiques                         | 84  |

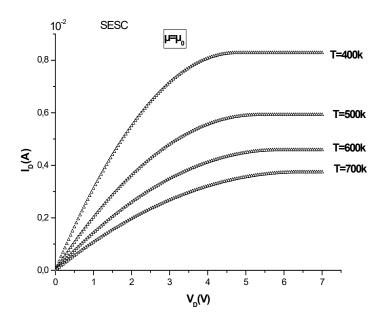

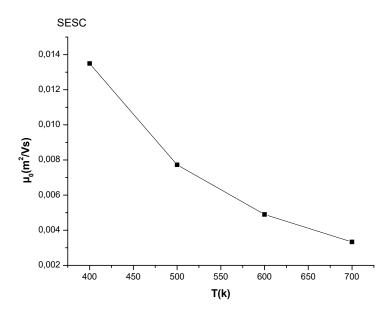

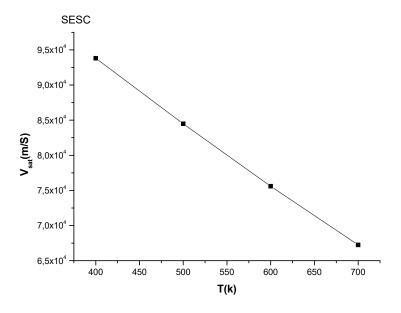

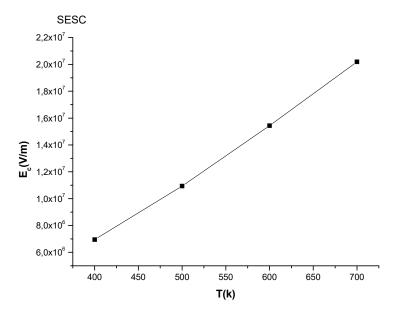

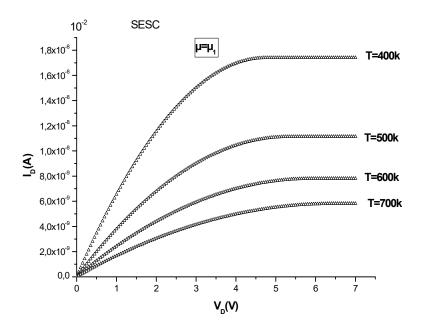

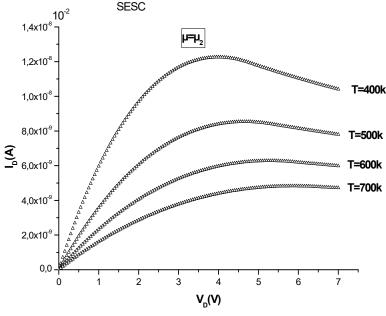

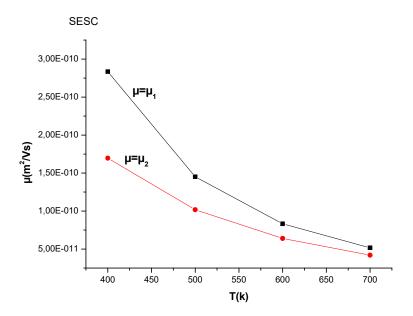

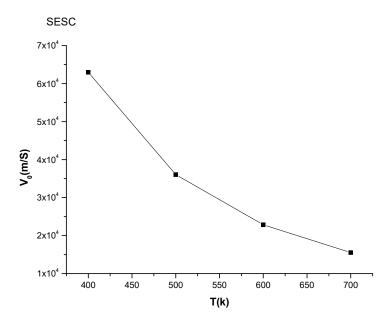

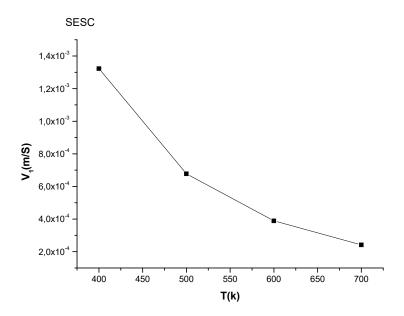

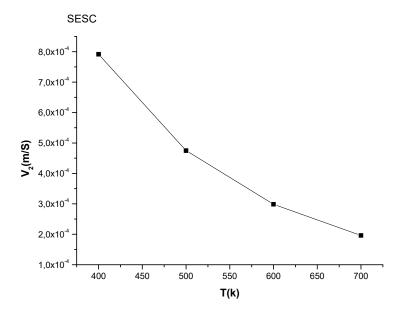

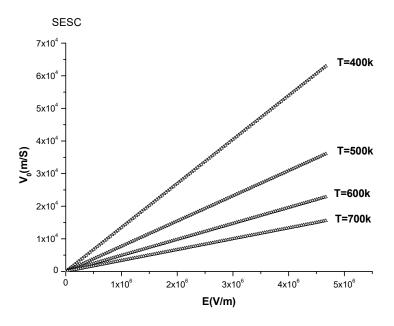

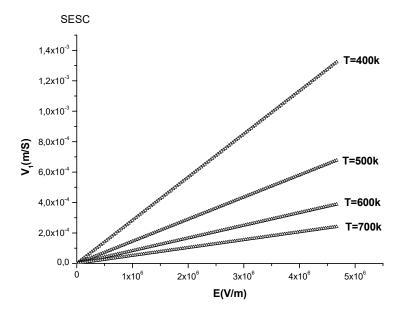

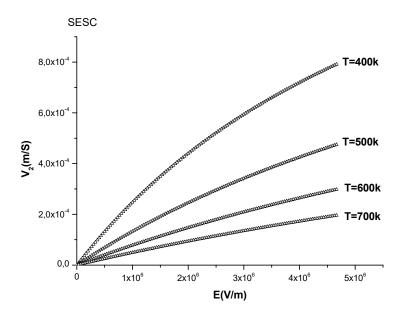

| IV.2.6 Effet de la température                           | 75  |

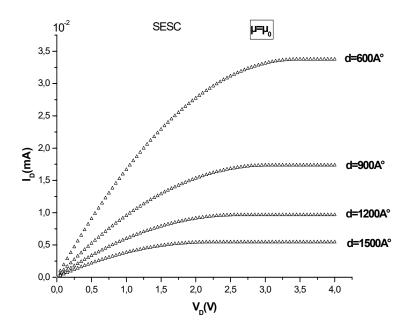

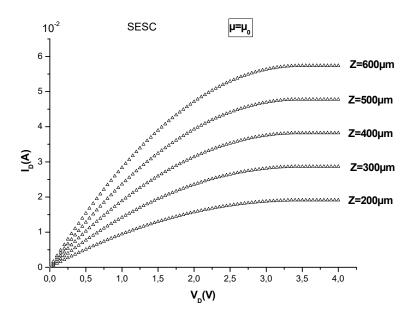

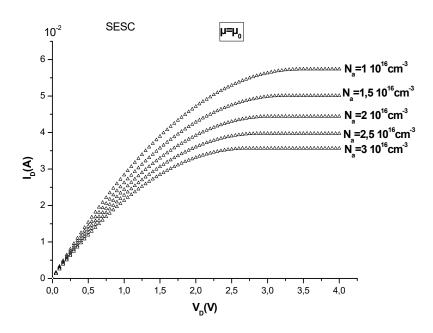

| IV.2.5 Effet des paramètres géométriques et physiques    | 71  |

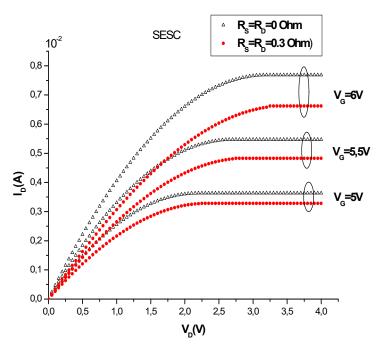

| IV.2.4 Effet des résistances parasites                   | 70  |

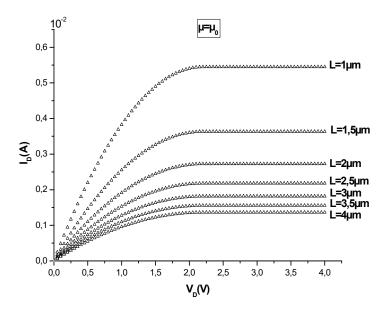

| IV.2.3 Effet de la mobilité variable                     | 64  |

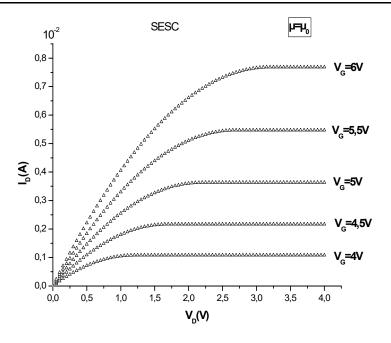

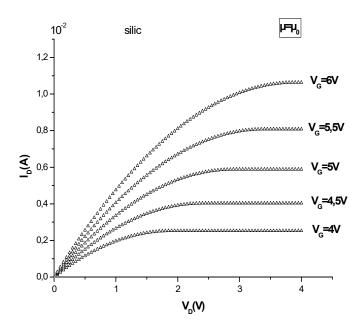

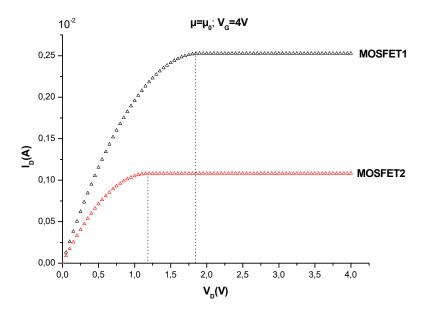

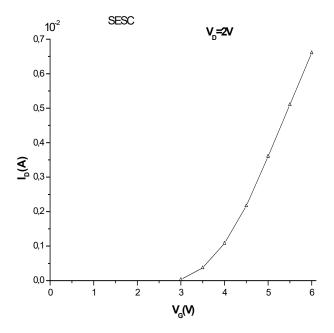

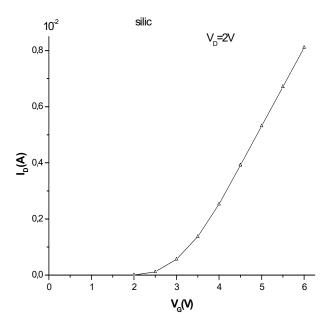

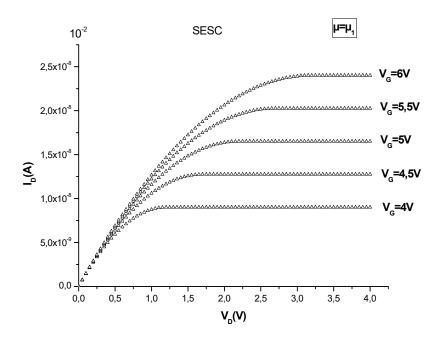

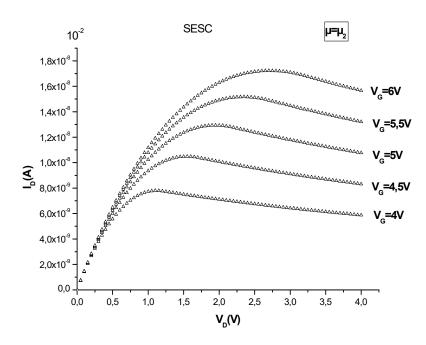

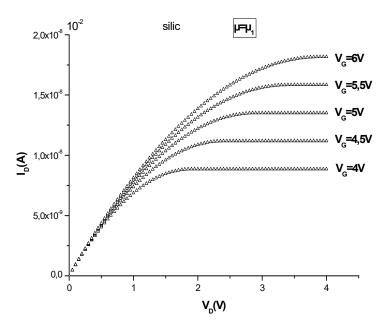

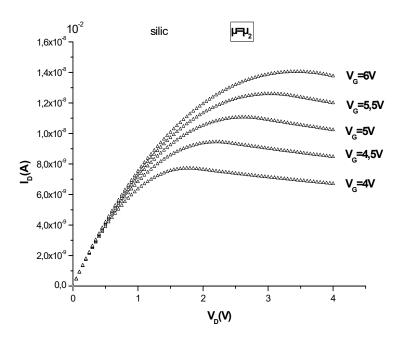

| IV.2.2 Caractéristiques courant tension I-V              | 61  |

#### **Introduction générale**

Accroître les performances, repousser les limites de l'impossible sont le but quotidien du chercheur. Dans l'univers de l'électronique, le développement de programmes militaires et spacieux a largement contribué à cette évolution. Aujourd'hui, d'autres domaines comme les télécommunications, l'informatique, les transports ou encore l'électronique, prennent une place très importante dans les activités de recherches des différents laboratoires. Cette course effrénée à l'amélioration des systèmes, les vitesses de plus rapides des calculateurs numériques, ou les quantités des informations véhiculées par voie hertziennes toujours plus importantes, ont nécessité et nécessitent une montée en fréquence régulière des dispositifs concernés. Cette évolution fréquentielle requiert sans cesse une adaptation des composants électroniques.

Le MOSFET a été conçu de façon théorique en 1920 par Julius Lilienfeld qui le breveta comme étant un composant servant à contrôler le courant [1]. Par contre, la technologie nécessaire à sa construction ne fut pas disponible avant 1950. Effectivement, la complexité du MOSFET requiert des techniques plus précises que ce qui était disponible à l'époque. Ce ne fut qu'avec l'avènement des circuits intégrés que le MOSFET put devenir une réalité. Ainsi, Attalla et Khang des laboratoires Bell construisent le premier MOSFET en 1959 qui fera son apparition dans les circuits intégrés en 1963. Peu après, l'élaboration de la technologie CMOS assura le futur commercial et technologique du MOSFET en électronique intégrée [2,3].

Le transistor MOS est de loin, le dispositif le plus répondu dans la production actuelle de composants semiconducteurs, car il est le composant de base de la technologie CMOS (complementary MOS), qui, à elle seule, englobe plus de 70 % de la production mondiale de circuits intégrés. Plusieurs sigles plus ou moins justifiés sont utilisés dans la littérature pour décrire le transistor MOS (Metal Oxide Semiconductor) : MOSFET (MOS Field Effect Transistor), IGFET (Insulated Gate Field Effect Transistor) et MOST (Metal Oxide Semiconductor Transistor)[4].

TMOS se caractérise par le fait que la *grille*, par l'effet de champ électrique, contrôle à travers l'oxyde de grille la densité de porteurs dans le canal du dispositif et ainsi l'intensité du courant dans le canal. Le canal est relié de part et d'autre à deux régions fortement dopées *drain* et *source* entre lesquelles est appliquée une tension donnant lieu à la circulation du courant [4].

Contrairement au transistor bipolaire, le transistor MOSFET fait appel à un seul type de porteur de charge c'est donc un composant unipolaire. En l'absence de phénomènes de stockage de porteurs minoritaires, les composants unipolaires sont intrinsèquement plus rapides. Deux avantages connexes doivent être soulignés [5] :

- ➤ Une très forte résistance d'entrée des dispositifs commandés, grâce à la possibilité de contrôler le flux de porteurs majoritaire par effet de champ.

- ➤ Une très grande stabilité thermique latérale sous polarisation directe en raison du coefficient de température négatif de la mobilité des porteurs, cette stabilité autorise la réalisation de composants de fort calibre en courant, avec une très grande surface active, par intégration parallèle de cellules élémentaires.

Les progrès technologiques ont permis de réduire les dimensions et notamment la longueur de grille, du MOSFET favorisent ainsi le fonctionnement en hautes fréquences. C'est ainsi que chaque innovation dans la réalisation du composant répond au désir de vérifier les avantages substantiels par des études théoriques qui prévoient de telles caractéristiques.

L'intérêt porté pour les technologies Si, et plus précisément pour les transistors MOS dans le domaine des RF, repose sur trois points [6] :

- ➤ Une technologie peu coûteuse par rapport aux technologies III-V. Elle est très mature d'un point de vue industriel.

- La quasi-totalité des circuits numériques sont réalisés avec cette technologie. On peut donc envisager des applications mixtes analogique/numérique sur la même puce (SoC : *System on Chip*).

- ➤ Elle requiert de faibles tensions de polarisation et présente une consommation en puissance très faible.

Et c'est là les points-clés qui ont poussé la recherche internationale à faire évoluer cette technologie dans les RF. C'est le candidat idéal pour toutes les applications où la faible consommation et la forte intégration sont exigées, par exemple pour toutes les applications embarquées.

Le travail qui fait l'objet de notre thèse est « l'étude des propriétés statiques et dynamiques du transistor à grille isolée MOSFET ». Ce travail comportera les chapitres suivants :

Le premier chapitre est consacré aux caractéristiques générales du MOSFET. On présentera un état d'art des composants à effet de champ, la structure et le principe de fonctionnement du MOSFET, ainsi que les propriétés physiques et électriques du Silicium « Si ».

Dans le deuxième chapitre on a étudié les propriétés statiques du transistor MOSFET. Une formulation analytique des principaux mécanismes statiques est effectuée et permet d'aboutir à un modèle mathématique du transistor MOSFET.

Le troisième chapitre est consacré aux propriétés dynamiques du composant MOSFET en hautes fréquences. Nous présenterons un schéma équivalent électrique petit signal. Les principaux paramètres du comportement dynamique seront décrits.

Le dernier chapitre de ce mémoire présente l'ensemble des résultats de la simulation des caractéristiques statiques et dynamiques des transistors MOSFET. Au cours de cette présentation, l'interprétation des résultats obtenus est faite en détaille.

Une conclusion générale et des perspectives à ses travaux seront indiquées en fin de ce manuscrit.

# CHAPITRE I

# Caractéristiques générales du MOSFET

#### I.1 Introduction

Aujourd'hui le transistor MOS constitue, par sa simplicité de fabrication et ses petites dimensions, l'élément fondamental des circuits intégrés numériques à large échelle.

Le but de ce premier chapitre est de présenter la structure et le principe de fonctionnement du transistor MOSFET, ainsi que les phénomènes physiques internes au composant qui régissent son fonctionnement. Aussi une étude sur les propriétés physiques et électriques du Silicium « Si » est présentée.

#### I.2 Etat de l'art des transistors

Le transistor est le composant électronique actif fondamental en électronique utilisé principalement comme interrupteur commandé pour l'amplification, mais aussi pour stabiliser, moduler un signal ainsi que de nombreuses autres utilisations.

Le terme transistor provient de l'Anglais transconductance varistor (résistance variable de transconductance). Le transistor fut considéré comme un énorme progrès face au tube électronique : il est plus robuste, il fonctionne avec des tensions faibles, il peut donc être alimenté par des piles et il fonctionne instantanément une fois mis sous tension, contrairement aux tubes électroniques qui demandaient une dizaine de secondes de chauffage. Il a été rapidement assemblé, avec d'autres composants, au sein de circuits intégrés, ce qui lui permit de conquérir encore plus de terrain sur les autres formes d'électroniques actives.

Le transistor a constitué une invention déterminante sans laquelle l'électronique et l'informatique ne posséderaient pas leurs formes actuelles (2007), il a permis à la société de l'information électronique de se développer.

Les transistors se classent en différentes familles et types. Le tableau (1) offre un classement des différents transistors ainsi que de leur composition [7].

| Type de transistor                         |                            | Structure      | Fonctionnement                               | Mécanisme<br>de contrôle                                         | Porteurs de<br>charge                                       |                                                             |

|--------------------------------------------|----------------------------|----------------|----------------------------------------------|------------------------------------------------------------------|-------------------------------------------------------------|-------------------------------------------------------------|

| Bipolaire<br>=<br>Transistor<br>à jonction | PNP                        |                | Jonctions<br>PN                              | Polarisation<br>directe ou<br>inverse des<br>jonctions           | Courant<br>circulant à<br>travers les<br>jonctions          | Electrons et<br>trous<br>Majoritaires<br>et<br>minoritaires |

| Unipolaire = A effet de champ = F.E.T      | Junction FET = JFET        | JFET<br>MESFET | Jonction PN  Jonction  Métal  Semiconducteur | Elargissement<br>de<br>la zone de<br>déplétion de la<br>jonction | Tension sur la grille séparée du canal par des jonctions    | Electrons ou<br>trous<br>Majoritaires                       |

|                                            | Insulated Gate FET = IGFET | MOS            | MIS                                          | Polarisation de<br>la grille isolée                              | Tension sur la grille isolée du canal par un isolant (SiO2) |                                                             |

Tableau (1) : Différents types de transistors

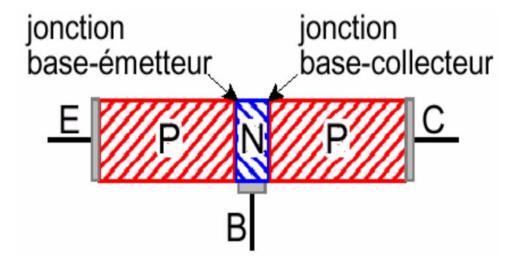

#### I.2.1 Transistors bipolaires

Les transistors bipolaires ont été les premiers à être utilisés. Le terme bipolaire provient de la présence des deux types de porteurs de charge dans le courant de sortie, les majoritaires et les minoritaires. Toutefois, la présence de deux types de porteurs de charge favorise les recombinaisons entre eux, cela augmente le temps de basculement entre deux états. De plus, les deux jonctions PN forment des capacités que doivent être vidées lors de la commutation. Cela ralentit encore le fonctionnement. Le transistor bipolaire est donc de moins en moins utilisé actuellement. La commande des transistors bipolaires est en courant électrique. Selon la valeur de ce courant, le transistor fournit ou non un courant de sortie. Il s'agit donc d'une source de courant commandée en courant [8].

Il est également appelé transistor à jonctions. Il est en effet composé de deux jonctions PN mise bout à bout. Ses deux types sont PNP et NPN selon l'alternance des zones semi-conductrices figure (I.1).

Figure (I.1): Transistor bipolaire PNP

#### I.2.2 Transistors unipolaires (transistor à effet de champ)

Les transistors unipolaires sont apparus par la suite. Ils sont caractérisés par la présence d'un seul type de porteurs de charge pour le courant, d'où leur nom d'*unipolaire*. Les transistors unipolaires sont également appelés *transistors à effet de champ, FET*. Le transistor fonctionne avec l'application d'un champ électrique. Ce champ rendra le transistor passant ou non. Les transistors unipolaires sont donc des sources de courant commandées en tension. Pour avoir un transistor à effet de champ, il faut que la borne de commande soit isolée des autres pour qu'un courant ne puisse circuler.

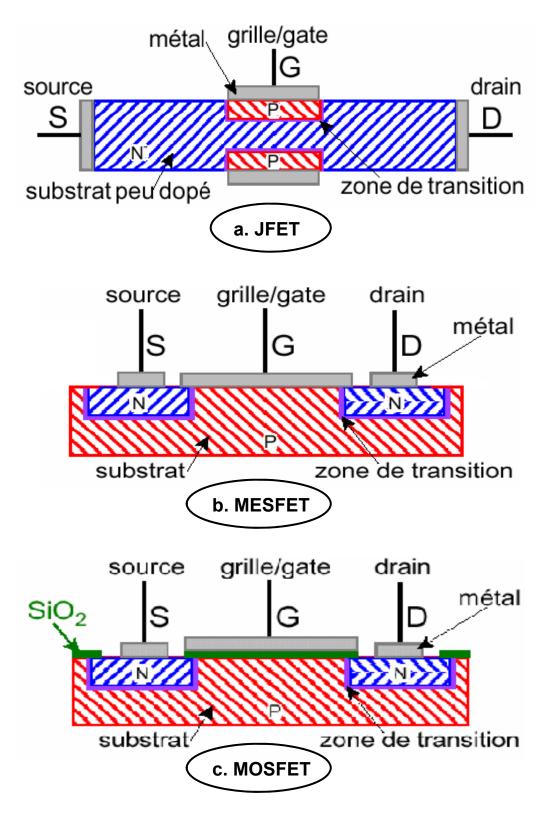

Il existe principalement trois groupes dans la famille des transistors à effet de champ FET [4]:

- **A.** *JFET* (*Junction FET*): dont l'effet de champ provient d'une jonction PN polarisée en inverse ; si la région P est la grille, elle module l'épaisseur du canal (région N) et, ainsi, son courant par l'extension de la zone de charge d'espace sous l'effet de la polarisation inverse de la jonction figure (I.2.a).

- **B**. *MESFET (Metal Semiconductor FET)*: dont l'effet de champ provient d'une jonction Schottky (métal-semi-conducteur) polarisée en inverse, le fonctionnement de la grille métallique étant analogue à celui de la grille du JFET figure (I.2.b).

- C. IGFET (Isulated Gate FET): dont l'effet de champ provient d'une grille isolée du canal par un diélectrique mince; actuellement, le diélectrique utilisé presque exclusivement, est l'oxyde SiO<sub>2</sub> d'où la dénomination MOSFET; cependant il faut remarquer que d'autres diélectriques, comme Si<sub>3</sub> N<sub>4</sub>, un empilement SiO<sub>2</sub> /Si<sub>3</sub> N<sub>4</sub> ou un empilement SiO<sub>2</sub> /Ta<sub>2</sub> O<sub>5</sub>, peuvent aussi être utilisés figure (I.2.c).

Des trois composants cités précédemment, le transistor MOS (IGFET ou MOSFET) est le dispositif le plus répondu dans la production actuelle de composant semi-conducteur, il est aussi le composant de base de la technologie CMOS (Complementary MOS). Le transistor MOSFET est l'objet de notre étude dans cette thèse.

Figure (12) : Structure différents types de transistors.

- a. Transistor JFET avec deux jonctions PN.

- b. Structure physique d'un transistor MESFET.

- c. Structure physique d'un transistor MOSFET.

#### I.2.3 Autres transistors

Il existe d'autres transistors [4] :

- **A.** *IGBT* (*Insulated Gate Bipolar Transistor*): Hybride qui a les caractéristiques d'un transistor à effet de champ en entrée et les caractéristiques d'un transistor bipolaire en sortie. Uniquement utilisé dans l'électronique de puissance.

- **B**. *Transistor unijonction*: Ce transistor est utilisé pour ses caractéristiques de résistance dynamique négative, ce qui permet de réaliser simplement un oscillateur. Il n'est plus utilisé de nos jours.

- C. *Phototransistor*: C'est un transistor bipolaire, dont la jonction base-collecteur est sensible à la lumière. Par rapport à une *photodiode*, il est plus sensible, car il bénéficie de l'effet amplificateur propre au transistor.

- **D.** Opto-isolateur: Le phototransistor est monté dans le même boîtier qu'une diode électroluminescente. C'est la lumière qui assure la transmission des signaux entre le phototransistor et la diode électroluminescente. Le pouvoir d'isolation très élevée (de l'ordre de 5 KV) en fait le composant idéal pour isoler galvaniquement un circuit de commande, d'un circuit de puissance. Il existe aussi des opto-isolateurs utilisant d'autres composants en sortie le **Thyristor**, le **Triac**.

#### I.3 Présentation du transistor MOSFET

Le transistor MOSFET (Métal Oxyde Semiconducteur Field Effect Transistor) est un dispositif unipolaire, le courant n'est assuré que par un seul type de porteur : électron pour les NMOS, trous pour les PMOS.

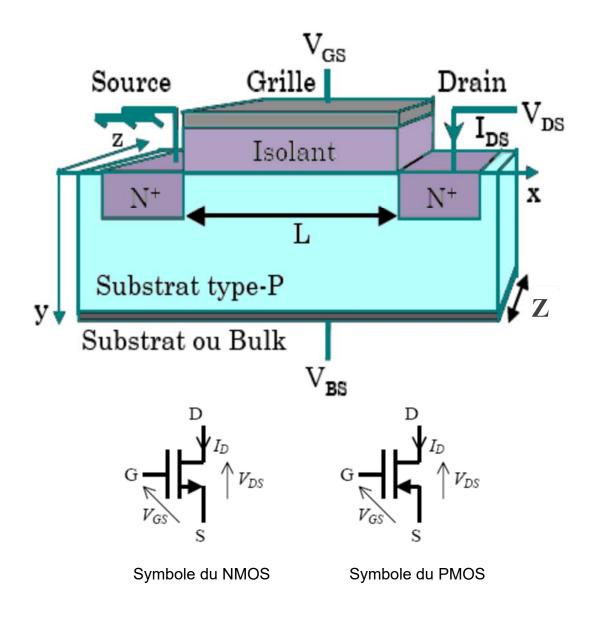

La structure basique d'un transistor MOS est représentée sur la figure (I.3). Le transistor est essentiellement constituée d'un substrat, généralement de type P, sur lequel on a fait croître une couche d'Oxyde de Silicium (SiO<sub>2</sub>). Au-dessus de la couche d'oxyde on place une *grille* métallique, de chaque côté de grille on place deux zone N<sup>+</sup> et des métallisations qui jouent le rôle de contact de *source* et de *drain*. Le rôle de ces deux électrodes est d'établir un champ électrique dans le canal et de recueillir le courant. La grille constitue l'électrode de commande de la capacité MOS, qui est réalisé sur le substrat entre la source et le drain [9].

Les principaux paramètres géométriques du composant sont : L (longueur de grille, distance drain-source), Z (largeur transversale de la structure) et d (l'épaisseur d'oxyde). Dans les circuits intégrés, le transistor MOS est généralement isolé des composants voisins par des tranches d'isolation.

Figure (1.3): Structure et symbole du transistor MOS

En général, on relie la source et le substrat à la masse. On porte le drain à un potentiel supérieur de ceux de la source et du substrat, créant ainsi un champ électrostatique entre la source, le substrat et le drain.

Suivons le type des porteurs assurent le passage du courant on peut parler des transistors MOS à canal N (ou NMOS, conduction par électrons) et des transistors MOS à canal P (ou PMOS, conduction par trous) (Fig I.3)

Les deux types fondamentaux de MOSFET sont les MOSFET à appauvrissement (Deplition) **D-MOSFET**, et les MOSFET à enrichissement (Enhancement) **E-MOSFET** [10] :

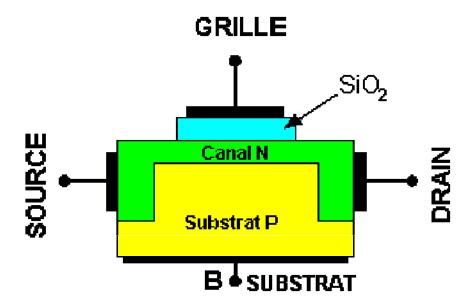

#### I.3.1 D-MOSFET

Le drain et la grille sont reliés par un canal étroit du même type (N pour, P pour D-MOSFET canal N) (Fig I.4).

Dans le cas du D-MOSFET canal N, si on applique une tension négative sur la grille par rapport au substrat, les électrons sont repoussés et la conductivité du canal diminue.

Figure (I.4) : Structure du MOS à appauvrissement canal N

#### I.3.2 E-MOSFET

Le drain et la grille ne sont pas reliés par un canal du même type (Fig I.5). Dans le cas de l'E-MOSFET canal N, si on applique une tension positive sur la grille par rapport au substrat, les électrons sont attirés à l'interface isolant-semiconducteur et les trous sont repoussés. A partir d'une certaine valeur de tension de seuil, une couche d'inversion apparaît et le transistor devient de plus en plus passant. Sans tension de commande, le E-MOSFET est bloqué (Normally off).

Figure (I.5) : Structure du MOS à enrichissement canal N

Dans les deux cas, le courant drain-source est modulé par la tension de grille. Dans le type à enrichissement il faut appliquer une tension positive à la grille pour amener la capacité grille-substrat en inversion ; le transistor conduit à partir d'un certain seuil. Dans le type à déplétion, le transistor est conducteur lorsque la grille est reliée à la masse, il faut donc l'amener à une tension négative pour faire cesser la conduction.

#### I.4 Généralités sur la structure MOS

La structure MOS est une structure du type M.I.S. (Métal Isolant Semiconducteur). Elle est l'élément actif d'un transistor MOSFET [11].

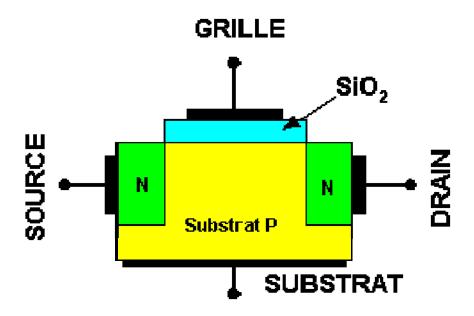

#### I.4.1 Diagramme d'énergie d'une structure Métal-Vide-Semiconducteur

On considère un métal, caractérisé par un travail de sortie  $q\Phi_m$  et un semiconducteur de travail de sortie  $q\Phi_s$ , séparés par un isolant constitué par une épaisseur de vide relativement faible (Fig I.6 gauche). Si le métal et le semiconducteur sont reliés électriquement (Fig. I.6 droite), ils constituent un seul système thermodynamique, leurs niveaux de Fermi s'alignent et une différence de potentiel, analogue à la tension de diffusion du contact métal-semiconducteur, est créée par les différences des travaux de sortie apparaît :

$$qV_b = q\phi_s - q\phi_m \tag{1.1}$$

Figure (I.6): Structure métal-vide-semiconducteur.

- métal et semiconducteur isolé (gauche).

- métal et semiconducteur relié (droite).

La structure se comporte comme un condensateur plan dont la tension entre les armatures est constante (V<sub>b</sub>). La charge dépend de la capacité ou en d'autre terme de la distance entre les armatures. Si cette distance diminue, la capacité, et par conséquent la charge, augmente. Compte tenu de la forte densité d'états disponibles dans le métal, cette charge sera confinée sur une fraction de couche atomique (épaisseur supposée nulle). La charge dans le semiconducteur résulte de la variation de la densité de porteurs libres, électrons ou trous, au voisinage de la surface. La variation de la densité de porteurs libres est associée à la différence d'énergie entre le niveau de Fermi et les bandes de conduction ou de valence. Dans la mesure où le niveau de Fermi est fixé par l'équilibre thermodynamique, il en résulte une courbure des bandes de valence et de conduction vers le bas ou le haut, en fonction de l'augmentation ou de la diminution de la densité d'électrons. La nature de la charge d'espace et de la courbure des bandes est fonction du type du semiconducteur et de la différence des travaux de sortie.

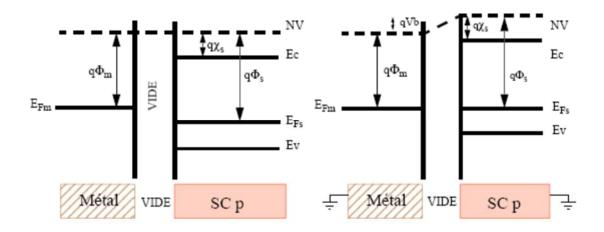

#### I.4.2 Diagramme d'énergie d'une structure MOS

En technologie silicium, l'isolant le plus couramment utilisé est l'oxyde de silicium. L'isolant, supposé parfait, est caractérisé par un gap  $E_g$  et par une affinité électronique  $q\chi_i$ . Le diagramme de bande sera similaire à celui de la Figure (I.6).

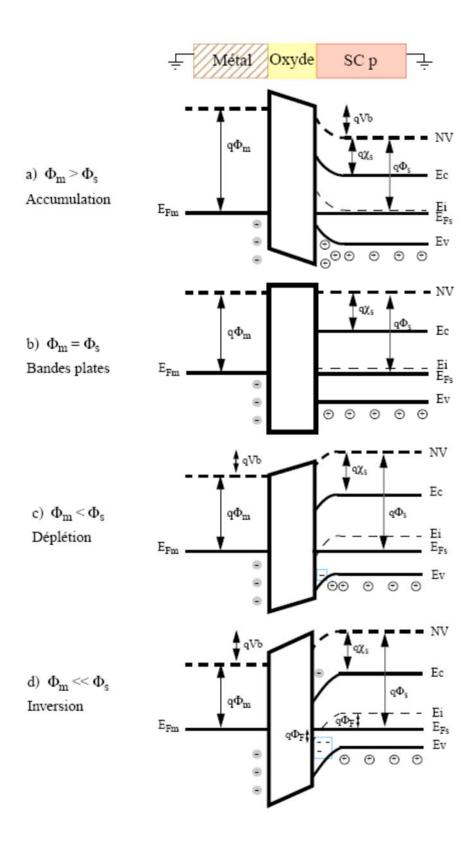

On considère un semiconducteur de type p (Fig. I.7) et différentes valeurs relatives des travaux de sortie du métal et du semiconducteur :

#### a) Accumulation $(\phi_m > \phi_s)$

Si V<sub>b</sub> est positif, des charges positives se développent dans le semi-conducteur et des charges négatives dans le métal. Les charges négatives dans le métal résultent d'une accumulation d'électrons à la surface. Les charges positives dans le semi-conducteur résultent d'une accumulation de trous à l'interface oxyde/SC, la bande de valence et la bande de conduction se courbent vers le haut. Le semi-conducteur est dit en *régime d'accumulation* (Fig I.7.a).

#### b) Bandes plates $(\phi_m = \phi_s)$

La tension de diffusion est nulle, aucune charge n'apparaît, les bandes restent horizontales, le semi-conducteur est dit en *régime de bandes plates* (Fig I.7.b).

#### c) Déplétion $(\phi_m < \phi_s)$

Si V<sub>b</sub> est négatif, des charges négatives se développent dans le semi-conducteur et des charges positives dans le métal. Les charges positives dans le métal résultent d'un départ d'électrons de la zone située au voisinage de l'interface. Les charges négatives dans le semi-conducteur résultent du départ de trous et proviennent d'une part de la présence d'ions accepteurs non compensés par la charge électronique correspondante, et d'autre part de l'augmentation de la concentration en porteurs minoritaires. A l'augmentation de la densité électronique est associée une courbure des bandes vers le haut.

Si la courbure de bande est relativement faible, la densité d'électrons reste inférieure à n<sub>i</sub>, les ions accepteurs constituent alors l'essentiel de la charge d'espace, le semi-conducteur est dit en *régime de déplétion* (Fig.c).

#### d) Inversion ( $\phi_m \ll \phi_s$ )

Si la courbure de bande est plus importante, la densité d'électrons augmente et lorsqu'elle devient supérieure à n<sub>i</sub>, le semi-conducteur devient de type n au voisinage de la surface, on dit que le semi-conducteur est *en régime d'inversion* (Fig I.7.d)

Figure (I.7) : Structure métal-oxyde-semiconducteur de type p à l'équilibre.

#### I.4.3 Effet d'une polarisation du matériau de grille

En pratique, le matériau de grille, dans la plupart des cas, a un niveau de Fermi différent de celui du silicium. Il faut donc appliquer une tension extérieure à la grille afin de rétablir une situation d'équilibre dans laquelle les bandes sont plates. Au premier ordre, cette tension de bandes plates (Flat Band) est égale à  $V_{FB}=\Phi_m-\Phi_s$ , sans prendre en compte les charges d'interface. Cependant, la différence de potentiel qui existe entre le métal et le semiconducteur peut avoir deux origines : d'une part la différence de travaux de sortie entre les deux matériaux ( $\Phi_{ms}$ ) et d'autre part la polarisation éventuelle d'un matériau par rapport à l'autre ( $V_G$ ). Ces deux effets s'additionnent pour donner le gradient de potentiel total :  $\Phi_{ms}+V_G$ . Sous l'action de cette polarisation, la structure évolue de manière analogue à la représentation faite en figure (I.7), d'un régime d'accumulation ( $\Phi_{ms}+V_G<0$ ) à un régime d'inversion ( $\Phi_{ms}+V_G>0$ ) en passant par les régimes de bandes plates ( $\Phi_{ms}+V_G=0$ ) et de déplétion.

Outre la différence des travaux de sortie et la polarisation extérieure, un autre phénomène modifie la barrière de potentiel : la présence de charges localisées à l'interface isolant-semiconducteur. Ces charges d'interface Qss induisent dans le semi-conducteur une charge équivalente de signe opposé (Qsc=-Qss). Il existe donc entre le métal et le semi-conducteur une différence de potentiel additionnelle résultant de la présence de ces charges. Ainsi, en prenant en considération la différence des travaux de sortie et la présence des charges d'interface, la tension de polarisation nécessaire à l'établissement du régime de bandes plates s'écrit :

$$V_{ER} = \phi_{ms} - Q_{ss} / C_{OY} \tag{1.1}$$

Où Cox représente la capacité de la couche isolante par unité de surface.

On définit la tension de seuil à la structure,  $V_T$ , comme la tension de polarisation nécessaire à l'établissement du régime de forte inversion. C'est la valeur de la tension de commande  $V_G$  pour laquelle le potentiel de surface  $V_s$ =2 $\Phi_F$ . Le seuil de forte inversion correspond au régime où la charge d'inversion devient prépondérante. En dessous de ce seuil, les charges dans le semiconducteur sont essentiellement des charges de déplétion.

La profondeur de la zone de déplétion peut se calculer facilement. Dans le semiconducteur, en supposant un dopage homogène, la densité de charge de déplétion s'écrit :

$$\rho(x) = -qN_a \tag{1.2}$$

De sorte que l'équation de Poisson s'écrit :

$$\frac{d^2V(x)}{dx^2} = -\frac{\rho(x)}{\varepsilon_s} = \frac{qN_a}{\varepsilon_s}$$

(1.3)

L'équation (1.3) est intégrée une première fois avec la condition E=0 en x=W car W est la limite de la zone de charge d'espace puis une seconde fois avec la condition V=0 en x=W. Il vient :

$$V(x) = \frac{qN_a}{\varepsilon_s} (x - W) \tag{1.4}$$

En utilisant le potentiel à l'interface  $Si/SiO_2$  (en  $x=0,\ V=V_S$ ), la profondeur de la zone déplétée s'écrit :

$$W = \left(\frac{2\varepsilon_s}{qN_a}V_s\right)^{1/2} \tag{1.5}$$

La valeur maximale de la profondeur de déplétion est atteinte lorsque le seuil de forte inversion  $(V_s=2\Phi_F)$  est franchi.

$$W_{m} = \left(\frac{2\varepsilon_{s}}{qN_{a}}2\phi_{F}\right)^{\frac{1}{3}} \tag{1.6}$$

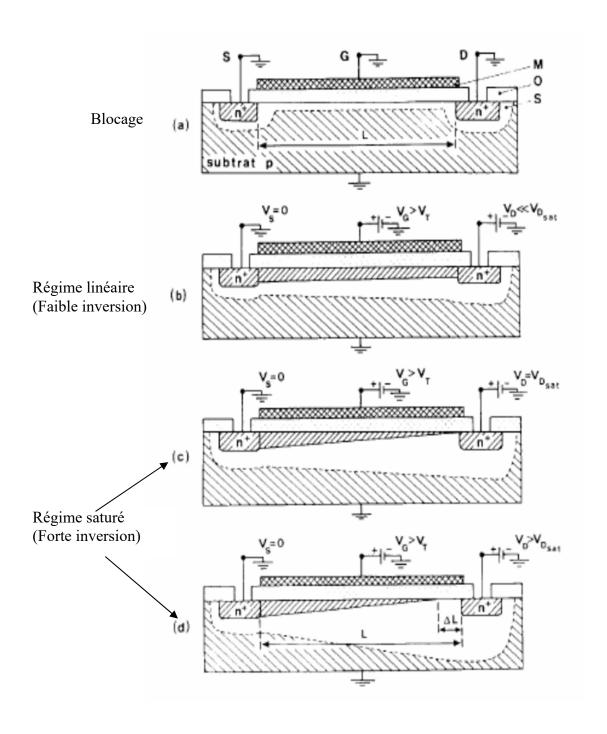

#### I.5 Principe de fonctionnement de MOSFET

Le fonctionnement d'un transistor MOSFET est assez simple à comprendre. Nous prendrons l'exemple d'un canal N le plus fréquent, le canal P à un fonctionnement identique en inverse les polarisations.

La figure (I.8) présente le principe de fonctionnement du transistor MOSFET à canal n à enrichissement. En l'absence de toute polarisation de la capacité MOS est en régime de déplétion, le transistor est normalement bloqué (Fig I.8.a). Une zone déplétée est aussi présente près des zones source et drain induites par la jonction p-n. Le transistor est polarisé dans l'état passant par

une tension grille-source V<sub>G</sub> positive, supérieure à la tension de seuil V<sub>T</sub> de la capacité MOS (Fig I.8.b). Une couche d'inversion de type n crée un canal conducteur qui relie la source et le drain. Le drain est polarisé positivement par rapport à la source par une tension V<sub>D</sub> et un courant I<sub>D</sub> circule dans le canal. La polarisation du drain produit une chute de potentiel entre la capacité MOS et le drain. La couche d'inversion devient moins importante coté drain alors qu'elle reste inchangée du coté source. De plus, cette couche d'inversion qui varie tout le long du canal, évolue avec la tension drain-source, ce qui entraîne une variation non linéaire du courant de drain [12].

#### • $V_D \ll V_{Dsat}$

Lorsque la tension de drain est faible, la variation de conductance du canal est négligeable, le courant de drain varie proportionnellement à la tension drain-source, le transistor fonctionne en *régime linéaire* (Fig I.8.b).

#### • $V_D \le V_{Dsat}$

Quand la tension drain augmente, il se produit une augmentation locale de la tension de seuil dans le canal jusqu'à une valeur particulière de V<sub>D</sub>, appelée tension de saturation, où la capacité MOS n'est plus en inversion. Un point de pincement se crée du côté du drain (Fig I.8.c). Le courant de drain amorce une saturation (I<sub>Dsat</sub>).

#### $\bullet$ $V_D > V_{Dsat}$

Quand la tension drain source augmente au-delà de la tension de saturation, la région voisine du drain n'est plus en inversion, le point de pincement se déplace vers la source (Fig I.8.d) et se trouve à une distance  $\Delta L$  du drain. Le courant est transporté par les porteurs libres jusqu'au point de pincement puis sont propulsés vers l'électrode de drain par le champ électrique qui existe dans la région désertée. La tension aux bornes du canal conducteur reste constante et égale à  $V_{Dsat}$ . Si la variation relative ( $\Delta L/L$ ) de la longueur du canal est faible, le courant de drain est égal à  $I_{Dsat}$  et indépendant  $V_D$ .

Figure (I.8): Principe de fonctionnement du transistor MOSFET

#### I.6 Silicium

Le silicium est un élément chimique de la famille des cristallogènes, de symbole Si et de numéro atomique14. Le nom dérive du latin *silex*, ce qui signifie caillou ou silex.

C'est l'élément le plus abondant sur la Terre après l'oxygène, soit 25,7 % de sa masse. Il n'existe pas à l'état libre mais sous forme de composés : sous forme de dioxyde, la silice (dans le sable, le quartz, la cristobalite, etc...) ou de silicates (dans les feldspaths, la kaolinite, etc.).

Il est utilisé depuis longtemps sous forme d'oxyde de silicium amorphe (silice ou SiO2) comme composant essentiel du verre. Il a de nouveaux usages en électronique, pour la production de matériaux tels que les silicones ou pour fabriquer des modules solaires photovoltaïques.

Les propriétés de semi-conducteur du silicium ont permis la création de la deuxième génération de transistors, puis les circuits intégrés (les « puces »). C'est aujourd'hui encore l'un des éléments essentiels pour l'électronique, notamment grâce à la capacité technologique actuelle permettant d'obtenir du silicium pur à plus de 99,99999% [13].

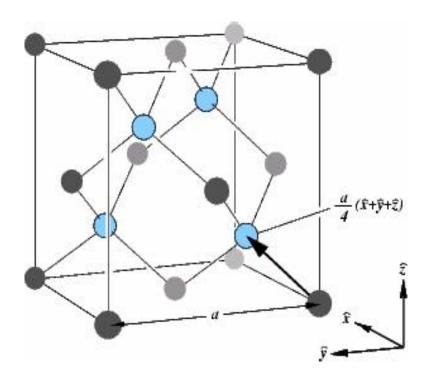

#### **I.6.1 Structure cristalline**

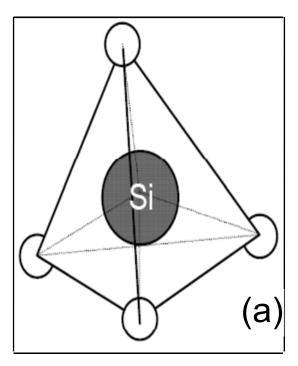

Le cristal de Silicium est formé d'un réseau de type cubique face centrée. Le motif est constitué de deux atomes de Silicium. Le réseau de Bravais formera donc deux réseaux CFC imbriqués. La longueur des vecteurs primitifs est de 543 pico mètres.

Nous voyons dans la figure (I.9) les deux réseaux CFC imbriqués, représentés respectivement en bleu et en gris. Le motif étant composé de deux atomes de Silicium, les noeuds de chacun des réseaux sont occupés par un atome de Si. Pour d'autres cristaux de semi-conducteur, tel que l'arséniure de Gallium, AsGa, un réseau est composé d'atomes d'Arsenic et l'autre d'atomes de Gallium.

Dans le cristal, chaque atome de Silicium est lié à 4 voisins par une liaison covalente. Cette liaison repose sur la mise en commun d'un électron de valence de chacun des deux atomes. Ces deux électrons sont répartis symétriquement entre les deux noyaux. Les deux électrons appartiennent à deux atomes et leur orbitale est donc appelée orbitale moléculaire. Cette liaison correspond à l'hybridation (une modification de sa forme suite à une interaction avec un autre atome ou molécule) des orbitales du Silicium. Elle est de type sp<sup>3</sup> [7,14].

Figure (I.9) : Réseau d'un cristal de Silicium.

Figure (I.10): Liaisons covalentes dans le cristal.

La couche de valence de l'atome de Silicium contenant 4 électrons, il pourra créer 4 liaisons avec des atomes voisins, en mettant à chaque fois un électron en commun. Chaque atome sera au centre d'un tétraèdre dont les sommets sont occupés par 4 autres atomes. Le cristal peut donc être assimilé à une molécule géante. Comme chaque électron de valence est mis en commun pour former une liaison, il n'y a plus d'électrons solitaires dans la couche de valence. Les quatre électrons de la bande de valence de l'atome qui sont utilisés pour les liaisons, et les quatre électrons provenant des autres liaisons forment un octet électronique qui sature la couche de valence de l'atome. Tous les électrons sont donc liés à des atomes particuliers et localisés près de ceux-ci figure (I.10).

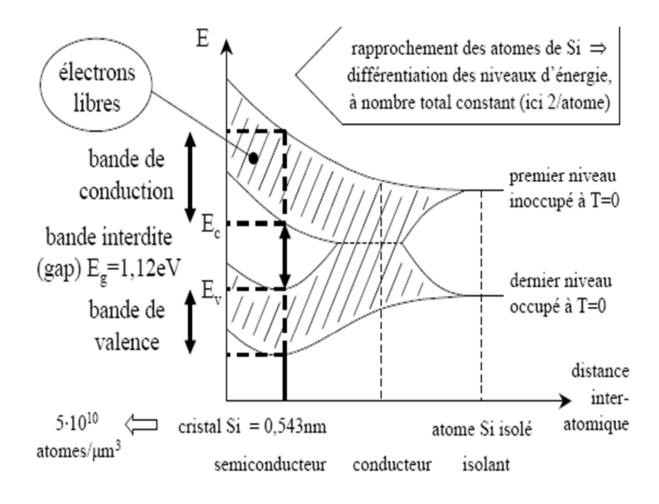

#### I.6.2 Bande d'énergie interdite

L'énergie de bande interdite mesure la quantité d'énergie nécessaire à un électron pour passer de la bande de valence à la bande de conduction lorsque celui-ci est soumis à une excitation.

Le silicium possède aussi une structure de bande d'énergie interdite directe figure (I.11), qui lui confère des propriétés d'absorption optique et de luminescence importantes susceptibles d'être exploitées en optoélectronique.

La taille de bande interdite donne des caractéristiques électriques importantes à chaque semiconducteur. En effet, la largeur de bande interdite fixe la limite en température au-dessous de laquelle le dispositif peut fonctionner sans détérioration, ainsi que l'aptitude du semiconducteur à résister aux radiations.

Les variations de la largeur de la bande interdite peuvent être décrites approximativement par la fonction [15, 16, 17] suivante pour des températures supérieures à 300 K :

$$E_G(T) = 1.17 - \left(\frac{4.73 \times 10^{-4} \times T^2}{636 + T}\right) (eV).$$

(1.7)

Figure (I11) : Bande d'énergie interdite du Silicium.

#### I.6.3 Propriétés physiques et électriques du silicium

Les propriétés physiques et électriques du silicium sont donnés dans le tableau (2) suivant [9, 16, 18].

| Propriétés                  | Silicium « Si »                                         |

|-----------------------------|---------------------------------------------------------|

| Masse volumique             | 2330 kg/m <sup>3</sup>                                  |

| Température de fusion       | 1687 K                                                  |

| Température de vaporisation | 3173 K                                                  |

| Permittivité                | 1.06 PF/cm                                              |

| Volume molaire              | 12.06 10 <sup>-6</sup> m <sup>3</sup> /mol              |

| Conductivité thermique      | 148 W/cm.K                                              |

| Conductivité électrique     | 2.52 10 <sup>-4</sup> Ω <sup>-1</sup> .cm <sup>-1</sup> |

| Energie de Gap              | 1.12 ev                                                 |

| Energie de fusion           | 50.55 kJ/mol                                            |

| Energie de vaporisation     | 324.22 kJ/mol                                           |

| Mobilité des Electrons      | 1430 cm <sup>2</sup> /V·S                               |

| Mobilité des trous          | 495 cm <sup>2</sup> /V·S                                |

| Pression de vapeur          | 4.77 Pa                                                 |

| <u></u>                     |                                                         |

Tableau (I2): Principales caractéristiques du Silicium.

#### I.6.4 Phénomènes de transport

#### I.6.4.1 Transport stationnaire

La conduction électrique et de manière plus générale, le transport, résultent d'une perturbation de l'équilibre thermodynamique du système. Lorsque le champ électrique (la perturbation) est maintenu constant, un état de déséquilibre permanent s'installe et crée un flux de porteurs. Un pseudo-équilibre thermodynamique stable est atteint et le transport est alors dit stationnaire [19].

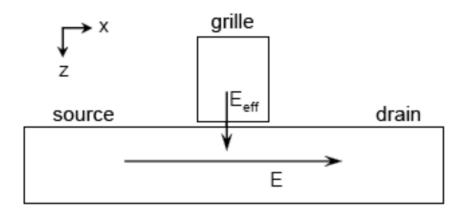

Figure (1.12): Principaux champs électriques dans un transistor.

- $E_{eff}$ : champ électrique vertical ou transverse

- E : champ électrique latéral ou longitudinal

#### a ) Conduction à faible champ latéral : Loi d'Ohm et mobilité

Pour des champs faibles (<10<sup>3</sup> V/cm), la loi d'Ohm s'applique :

$$\vec{J} = \sigma \vec{E} \tag{1.8}$$

Elle relie la densité de courant à sa cause, le champ électrique, par la conductivité :

$$\sigma = qn\mu_{eff} \tag{1.9}$$

Avec  $\mu_{eff}$  la mobilité effective à faible champ et n la densité surfacique de porteurs

$$\mu_{eff} = \frac{q\,\tau}{m_{cc}} \tag{1.10}$$

Avec  $\tau$  le temps moyen de relaxation entre deux collisions et  $m_{cc}$  la masse effective de conductivité des porteurs.

L'hypothèse de champ faible implique que lors du transport il n'y a pas d'échauffement des porteurs. Le taux d'augmentation d'énergie reste inférieur au taux de perte par interactions avec le réseau. L'énergie acquise par les porteurs entre deux collisions est en moyenne complètement perdue lors de la collision. Les porteurs se thermalisent et sont en équilibre thermodynamique avec le réseau.

La vitesse d'entraînement (ou de dérive) des porteurs est alors proportionnelle au champ électrique:

$$\vec{v}_{der} = \mu_{eff} \vec{E} \tag{1.11}$$

#### b) Conduction à fort champ latérale : saturation de la vitesse des porteurs

Dans les dispositifs submicroniques, pour une polarisation de drain de seulement 1V, le champ électrique résultant dépasse déjà  $10^4$  V/cm. Au-delà de  $10^3$  V/cm, la loi d'Ohm cesse d'être valable et la vitesse d'entraînement dans de tels composants n'est plus proportionnelle au champ électrique.

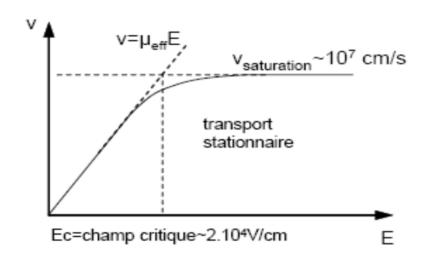

L'énergie des porteurs s'accroit, augmentant en même temps la fréquence des collisions, ce qui entraîne une chute de la mobilité puis une saturation de la vitesse de l'ensemble des porteurs. La vitesse présente donc en fonction du champ une loi de variation linéaire puis un régime de saturation (Fig I.13). Lorsque la perturbation est permanente (champ constant), un équilibre stable est atteint. La vitesse de saturation stationnaire atteinte alors par les porteurs (~10<sup>7</sup> cm/s) résulte d'un équilibre entre accélération par le champ et freinage par les collisions avec le réseau et les impuretés, et est indépendante de la polarisation de drain.

Figure (I.13): la variation de la vitesse d'entraînement des porteurs en fonction du champ électrique latéral.

- E < Ec, le transport est stationnaire et  $v = \mu_{eff}E$ .

- E>Ec, la vitesse sature à cause des interactions avec le réseau.

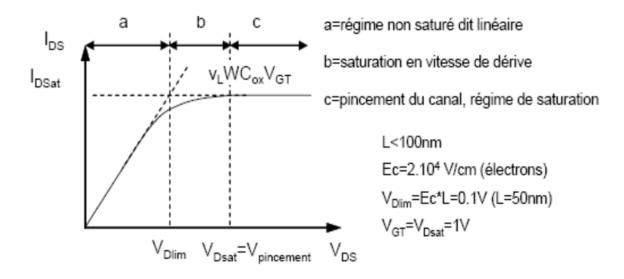

Cette saturation de la vitesse peut être atteinte pour une tension Drain-Source  $V_{DS}$  inférieure à la tension de pincement du canal au drain. En effet, partant du régime linéaire ou non saturé à  $V_{DS}$ < $V_{G}$ - $V_{th}$ = $V_{GT}$ , si le champ latéral E= $V_{DS}$ /L est suffisamment fort, comme dans le cas de transistors très courts, il causera une saturation en vitesse et donc la saturation du courant, et ce, avant même que le canal ne soit pincé à  $V_{DS}$ = $V_{GT}$ . La saturation en vitesse peut donc devancer

la saturation due au pincement du canal dans les transistors très courts (voir figure I.14). Ce problème est particulièrement d'actualité pour les transistors modernes dont la grille fait moins de 100nm. Les PMOS sont moins impactés que les NMOS car la mobilité des trous est plus faible que celles des électrons, le champ critique E<sub>c</sub> est donc d'autant plus élevé (figure I.13), ce qui fait que la vitesse des trous sature pour des longueurs de grille inférieures à celles des NMOS.

Figure (I.14) : Saturation du courant avant le pincement du canal. Le champ latéral est trop fort, même à  $V_{DS} < V_{GT}$ , et la vitesse sature (cas d'un NMOS).

#### I.6.4.2 Transport non stationnaire

Lorsque le champ varie fortement dans l'espace ou le temps, typiquement lorsqu'un porteur pénètre dans une région à fort champ, le phénomène de survitesse ou *velocity overshoot*, bien connu dans les semiconducteurs à gap direct (GaAs), apparaît dans le Si à température ambiante [20]. Il se caractérise par le fait que la vitesse d'une partie des porteurs est supérieure à la vitesse d'entraînement stationnaire correspondant à ce champ. La vitesse stationnaire est de nouveau obtenue au bout d'un certain temps. Le transport durant cette période est hors équilibre ou non stationnaire. Cela signifie que pendant un certain temps et donc sur une certaine distance, les porteurs ont une vitesse moyenne qui peut être sensiblement supérieure à la vitesse de dérive ou même à la vitesse de saturation. Cela est possible car le temps de relaxation nécessaire pour ramener le système à l'équilibre n'est pas nul. S'il était très faible, à cause par exemple d'un

nombre trop important d'impuretés dans le canal, l'équilibre serait maintenu et la survitesse n'aurait pas lieu.

Ce phénomène de transport non stationnaire peut donc se révéler très intéressant dans le cas d'un transistor fortement submicronique, à la condition qu'il se produise à l'entrée du canal (la source) : les porteurs sont en survitesse sur une grande partie voire même la totalité du canal de conduction. Le courant de drain est alors augmenté et sera sous estimé par le modèle de dérive-diffusion.

De plus, lorsque la longueur du canal approche le libre parcours moyen des porteurs, les probabilités d'interactions peuvent devenir très faibles et les porteurs peuvent traverser le canal sans aucune interaction.

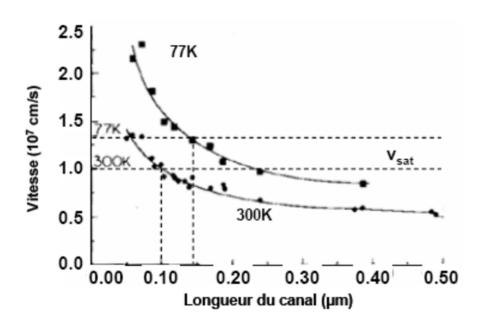

Figure (I.15): Vitesse effective des porteurs en fonction de la longueur du canal. Le phénomène de survitesse pour les électrons est observé à 77K pour des canaux inférieurs à 130nm et même à température ambiante pour des canaux inférieurs à 90nm. A 300K, la vitesse effective maximum obtenue vaut  $1.3\ 10^7\ cm/s > V_{sat}=10^7\ cm/s$ .

# I.7 L'Oxyde de Silicium SiO<sub>2</sub>

La silice est un composé chimique minéral (dioxyde de silicium) de formule SiO<sub>2</sub>.

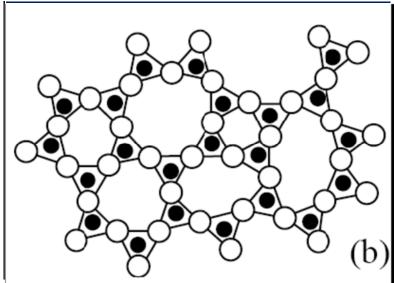

La silice peut se trouver sous différentes formes allotropiques (même composition chimique, mais arrangements atomiques différents) depuis le quartz (ordre cristallographique à longue distance) jusqu'à la silice amorphe (ordre à courte distance). La structure obtenue par oxydation thermique est amorphe. L'unité structurelle de base de la silice est un atome de silicium entouré de quatre atomes d'oxygène (SiO<sub>4</sub>) constituant les sommets d'un tétraèdre Figure (I.16).

La silice est constituée d'un arrangement de tétraèdres SiO4 reliés entre eux par l'intermédiaire d'un sommet oxygène. L'aspect plus ou moins aléatoire de la silice est introduit par la valeur de l'angle entre les liaisons Si-O-Si, qui peut varier de 110° à 180°. Il est de 144° dans le quartz [21].

La silice est aussi l'un des meilleurs isolants électriques qui existe.

On remarque que deux éléments jouent un rôle particulier : le Silicium et l'oxyde de Silicium. Bien qu'ayant considéré particulièrement le Silicium jusqu'à présent, le développement des circuits intégrés n'aurait pas été possible sans l'oxyde de Silicium. En effet, le procédé planar permet de n'utiliser qu'un seul matériau de base : le substrat. Sur celui-ci sont alors déposées d'autres couches. Celles-ci sont isolées les unes des autres à l'aide d'oxyde de Silicium. De même l'isolation des transistors à effet de champ MOS impose l'utilisation d'oxyde de Silicium.

Nous ne pouvons donc pas dissocier le Silicium et son oxyde lorsque nous évoquons l'utilisation dans les circuits intégrés. La caractéristique la plus intéressante de l'oxyde est la facilité à le faire croître directement sur la surface du Silicium [7].

Cet oxyde est utilisé comme un diélectrique isolant dans les circuits intégrés. Son gap est en effet extrêmement élevé. Il peut donc être considéré comme un isolant parfait grâce à sa résistance de 10<sup>15</sup> ohms. Cette résistivité permet d'isoler parfaitement la grille du MOS et rend ainsi la consommation statique des transistors MOS nulle. C'est une autre raison importante du développement massif des circuits intégrés à base de transistor MOS.

Cet oxyde est un isolant non cristallin, dense, uniforme et donc stable sur de larges variations de température. Couplé à la croissance aisée sur le wafer par simple exposition à l'oxygène, il rend le processus planar de fabrication des circuits intégrés facile à mettre en œuvre [7].

Figure (1.16): Structure de base du SiO<sub>2</sub>

(a)Motif de base de la silice.

(b)Représentation plane du réseau de la silice amorphe.

Les sphères blanches représentent les atomes d'oxygène.

# CHAPITRE II

# Propriétés Statiques du MOSFET

### **II.1 Introduction**

Un modèle analytique fiable permet de comprendre les phénomènes physiques qui sont à l'origine du comportement électrique du MOSFET.

Ce chapitre est consacré aux propriétés statiques du MOSFET. L'objectif visé est d'une part de déterminer les caractéristiques de sortie d'une structure MOSFET classique en zone ohmique et en zone saturée, donnée par la loi  $I_D$ = $f(V_G, V_D)$  est primordiale pour comprendre son comportement physique. D'autre part des expressions analytiques des différentes grandeurs caractéristiques tel que les résistances et la mobilité ainsi que leurs effets.

La température de fonctionnement du composant à une influence directe sur leurs caractéristiques. Alors, la prise en compte de l'effet thermique dans les MOSFET's est nécessaire.

### II.2 Tension de seuil

La tension de seuil ( $V_T$  Thershold voltage) une des notions les plus fondamentales pour un transistor MOS, car elle gouverne la mise en conduction du transistor parfois ;  $V_T$  est aussi appelée *tension de mise de conductions*.

La tension de seuil de la structure MOS est définie par la tension de polarisation de l'électrode métallique nécessaire à l'établissement du régime de forte inversion, c'est donc la valeur de la tension de grille à partir de laquelle le transistor commence à conduire (formation du canal d'inversion entre source est drain). Cette valeur dépend du dopage de la zone P, de l'épaisseur de l'oxyde de grille, et de la présence de charges à l'interface Si-SiO<sub>2</sub>.

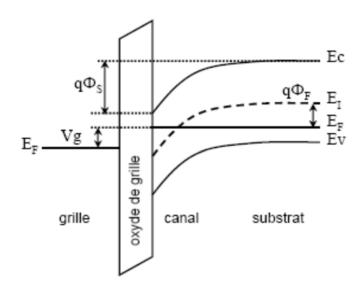

Sur la figure (II.1), la condition d'inversion forte est donc obtenue lorsque le potentiel de surface  $\Phi_S$  vaut deux fois le potentiel de Fermi  $\Phi_F$ , soit  $\Phi_S$ =  $2\Phi_F$ , avec [9, 12] :

$$\phi_F = \frac{kT}{q} \ln \left( \frac{N_a}{N_i} \right) \tag{2.1}$$

$O\dot{u}$ :  $N_a$ : la concentration de dopants dans le canal.

N<sub>i</sub>: la concentration intrinsèque de porteurs libres (N<sub>i</sub>=1.137 10<sup>10</sup> cm<sup>-3</sup> à 300k).

K : la constante de Boltzman.

T : la température.

e : la charge électrique.

Figure (II.1): Structure de bande NMOS.

L'expression de la tension de seuil est donnée ci-dessous [9, 12] :

$$V_T = 2\phi_{Fi} + \frac{\sqrt{4\varepsilon_s e N_a \phi_{Fi}}}{C_{ox}} + V_{FB}$$

(2.2)

$$C_{ox} = \frac{\varepsilon_{ox}}{d} \tag{2.3}$$

Avec : Cox : la capacité de l'isolant.

$\varepsilon_s$ ,  $\varepsilon_{ox}$  permittivité respectivement du silicium et de l'oxyde ( $\varepsilon_s$ =1.05  $10^{-12}$ F/cm,  $\varepsilon_{ox}$ =3.4531  $10^{-13}$ F/cm pour la silice).

d: l'épaisseur de l'oxyde de grille.

$$V_{FB} = \phi_{ms} - \frac{\phi_{ss}}{C_{cov}} \tag{2.4}$$

$O\dot{u}$ :  $V_{FB}$ : tension de bandes plates (Flat Band).

$\phi_{ms}$ : travail de sortie métal-semiconducteur.

φ<sub>ss</sub> : densité de charges d'interface.

$\frac{\phi_{ss}}{C_{ox}}$ : La tension correspondant à l'effet des charges à l'interface.

Dans le cas de la structure MOS idéale, les travaux de sortie du métal et du semiconducteur sont égaux. Il n'existe pas d'états d'interface entre l'isolant et le semiconducteur. L'expression de la tension devient :

$$V_T = 2\phi_{Fi} + \frac{\sqrt{4\varepsilon_s e N_a \phi_{Fi}}}{C_{ox}}$$

(2.5)

### II.3 Courant de drain

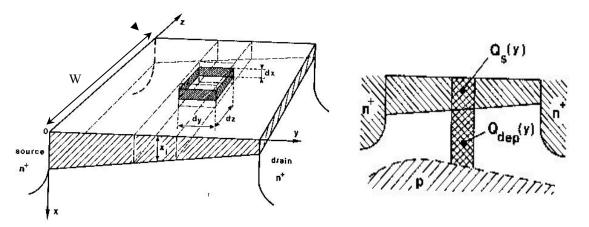

Pour calculer le courant de drain du MOSFET nous émettant les hypothèses suivantes [9, 12] :

- L'isolant (SiO2) est idéal : absence de charges pièges dans l'isolant et à l'interface du semi-conducteur. Il n'y a pas de différence de travail entre le métal et le semiconducteur.

- La mobilité des porteurs est constante dans la couche d'inversion.

- Le dopage du canal est uniforme dans tout le substrat

- Le courant de fuite est négligeable

- Approximation de la charge graduelle : Le champ transverse Ex dans le canal est plus important que le champ longitudinal Ey.

Considérons la figure (II.2), en un point de coordonnées xyz du canal conducteur, c'est-àdire de la couche d'inversion, la densité des électrons est n(xyz) et la conductivité du canal est donnée par :

$$\sigma(xyz) = e\mu n(xyz) \tag{2.6}$$

La conductance dans la direction source-drain (direction y) d'un élément de coordonnées xyz et de volume  $d\tau = dx dy dz$  est donnée par :

$$d^{3}g = \sigma(xyz)\frac{dxdz}{dy} = e\mu n(xyz)\frac{dxdz}{dy}$$

(2.7)

Compte tenu de la géométrie de la structure, la densité d'électrons est indépendante de z de sorte que l'intégrale sur z donne :

$$d^2g = Ze\mu n(xyz)\frac{dx}{dy}$$

(2.8)

Figure (II.2): Zone active du MOSFET. Figure (II.3): Densité surfacique de charges.

En intégrant cette expression sur toute la section conductrice du canal, c'est-à-dire de x=0 à  $x=x_i$ , où  $x_i$  représente la limite de la zone d'inversion, on obtient :

$$dg = Z\mu \frac{\int_{0}^{x_{i}} en(xyz)dx}{dy} = -Z\mu \frac{Q_{s}(y)}{dy}$$

(2.9)

Q<sub>s</sub>(y) représente la charge associée aux électrons présents sur toute la profondeur x<sub>i</sub> de zone d'inversion par unité de surface de structure, c'est la densité surfacique de charges d'inversion.

Cet élément de canal de longueur est étendu sur toute la section conductrice du barreau, il est donc parcouru par la totalité du courant de drain I<sub>D</sub>. la loi d'ohm aux bornes de cet élément de canal s'écrit donc :

$$I_D = dg \, dV \tag{2.10}$$

Où le courant de drain I<sub>D</sub> est conservatif c'est-à-dire constant avec y. En explicitant dg l'expression (2. 12) s'écrit :

$$I_D dy = -Z\mu Q_s(y)dV \tag{2.11}$$

On obtient le courant  $I_D$  en intégrant sur y de y=0 à y=L, et sur V de V=V<sub>s</sub>=0 à V=V<sub>D</sub>. Il faut au préalable expliciter la variation de  $Q_s(y)$ . En un point d'abscisse y de la structure (fig.II.3), la densité surfacique de charges du semiconducteur est donnée par :

$$Q_{sc}(y) = Q_{dep}(y) + Q_s(y)$$

(2.12)

Où  $Q_{dep}(y)$  représente la charge de déplétion et  $Q_s(y)$  la charge d'inversion.

La densité surfacique de charges participant au courant de drain, est par conséquent donnée par :

$$Q_{s}(y) = Q_{sc}(y) - Q_{dep}(y) \tag{2.13}$$

Si  $V_G$  est le potentiel de la grille et  $V_s(y)$  le potentiel de surface du semiconducteur à l'abscisse y, les densités surfaciques de charges développées à cette abscisse, dans le métal et dans la semiconducteur, sont données par :

$$Q_{m}(y) = -Q_{sc}(u) = C_{ox}(V_{G} - V_{s}(y))$$

(2.14)

L'étude de la structure MOS nous a montré qu'en régime forte inversion la différence entre la surface et le volume du semiconducteur restant sensiblement égale à  $2\phi_{Fi}$  (potentiel de fermi). La relation qui relie  $V_s(y)$  et V(y) le potentiel résultant de la polarisation drain source est la suivante :

$$V_s(y) - V(y) = 2\phi_{Fi} + 2\frac{kT}{e}\ln(V_g \approx 2\phi_{Fi})$$

(2.15)

Où : V<sub>g</sub> : tension de polarisation de la structure.

Alors:

$$Q_{sc}(y) = -C_{ox}(V_G - V(y) - 2\phi_{Fi})$$

La charge de déplétion est donnée pare :

$$Q_{dep}(y) = -eN_a W(y) = -(2eN_a \varepsilon_s(V_s(y) - V_{substrat}))^{1/2} = -(2eN_a \varepsilon_s V_s(y))^{1/2}$$

(2.16)

Avec:

W: la largeur de la zone de charge d'espace.

Soit en explicitant  $V_s(y)$ :

$$Q_{dep}(y) = -(2eN_a \varepsilon_s (V(y) + 2\phi_{Fi}))^{1/2}$$

(2.17)

Ainsi, par différence, on obtient l'expression de la densité surfacique de charges d'inversion en un point d'abscisse y :

$$Q_{s}(y) = -C_{os}(V_{G} - V(y) - 2\phi_{Ei}) + (2eN_{a}\varepsilon_{s})^{1/2}(V(y) + 2\phi_{Ei})^{1/2}$$

(2.18)

L'expression (2.13) s'écrit alors :

$$I_{D}dy = Z\mu C_{ox} \left( (V_{G} - V(y) - 2\phi_{Fi}) - \frac{(2eN_{a}\varepsilon_{S})^{1/2}}{C_{ox}} (V(y) + 2\phi_{Fi})^{1/2} \right) dV$$

(2.19)

En intégrant sur toute la longueur du canal, on obtient :

$$I_{D} = \frac{Z\mu C_{ox}}{L} \left( \left( V_{G} - \frac{V_{D}}{2} - 2\phi_{Fi} \right) V_{D} - \frac{2}{3} \frac{\left( 2eN_{a}\varepsilon_{S} \right)^{1/2}}{C_{ox}} \left( \left( V_{D} + 2\phi_{Fi} \right)^{3/2} - \left( 2\phi_{Fi} \right)^{3/2} \right) \right)$$

(2.20)

Cette expression peut se mettre sous la forme suivante :

$$I_{D} = K_{p} \left( \left( V_{G} - 2\phi_{Fi} \right) V_{D} - \frac{V_{D}^{2}}{2} - \frac{2}{3} \frac{\left( 2eN_{a}\varepsilon_{S} \right)^{\frac{1}{2}}}{C_{ox}} \left( 2\phi_{Fi} \right)^{\frac{3}{2}} \left( \left( 1 + \frac{V_{D}}{2\phi_{Fi}} \right)^{\frac{3}{2}} - 1 \right) \right)$$

(2.21)

K<sub>p</sub> étant le facteur de pente donné par :

$$K_{p} = \frac{Z\mu C_{ox}}{L} \tag{2.22}$$

Cependant, cette équation qui détermine la variation du courant de drain en fonction des deux tensions de polarisation ( $V_D$ ,  $V_G$ ) se réécrit différemment, selon le régime de fonctionnement du transistor et qui dépend essentiellement de la valeur de la tension de drain  $V_D$ .

Ces régimes sont :

- Régime linéaire, où le courant de drain varie linéairement avec la tension de drain V<sub>D</sub>.

- Régime de saturation, le courant se sature à la valeur I<sub>Dsat</sub>.

## II.3.1 Régime linéaire

La tension de drain dans ce régime obéit à la condition suivante :

$$V_{D} \leq V_{G} - V_{T} \tag{2.23}$$

On peut développer le terme en  $(1+\epsilon)^{3/2} \approx 1+3\epsilon/2$ , on obtient :

$$I_{D} = K_{p} \left( (V_{G} - 2\phi_{Fi}) V_{D} - \frac{V_{D}^{2}}{2} - \frac{2}{3} \frac{(2eN_{a}\varepsilon_{S})^{1/2}}{C_{ox}} (2\phi_{Fi})^{3/2} \frac{3}{2} \frac{V_{D}}{2\phi_{Fi}} \right)$$

(2.24)

Soit:

$$I_D = K_p \Biggl( \Biggl( (V_G - 2\phi_{Fi}) - \frac{(2eN_a \varepsilon_S 2\phi_{Fi})^{1/2}}{C_{ox}} \Biggr) V_D - \frac{V_D^2}{2} \Biggr)$$

(2.25)

Ou en posant:

$$V_T = 2\phi_{Fi} + \left(4eN_a\varepsilon_s\phi_{Fi}\right)^{1/2}/C_{ox} \tag{2.26}$$

$$I_{D} = K_{p} \left( (V_{G} - V_{T}) V_{D} - \frac{V_{D}^{2}}{2} \right)$$

(2.27)

$V_T$  correspond à l'expression que nous avons déjà établie (2.5), c'est la tension de seuil du transistor. C'est la valeur de la tension de grille qui crée dans le semiconducteur un potentiel de surface  $V_s=2\Phi_{Fi}$ , nécessaire à l'établissement du régime de forte inversion.

### II.3.2 Régime saturé

Quand la tension drain-source augmente au-delà du régime linéaire ( $V_D > V_G - V_T$ ), la densité surfacique de porteurs libres décroît au voisinage du drain et le courant présente une variation sous-linéaire avant d'atteindre un régime de saturation.

On obtient la tension de saturation  $V_{Dsat}$  en écrivant que pour  $V_D = V_{Dsat}$ ,  $Q_s(y) = 0$  en y = L. l'expression (2.18) s'écrit alors :

$$0 = -C_{ox}(V_G - V_{Dsat} - 2\phi_{Fi}) + (2eN_a \varepsilon_s)^{1/2} (V_{Dsat} + 2\phi_{FI})^{1/2}$$

(2.28)

Soit

$$V_{G} = V_{Dsat} + 2\phi_{Fi} + \frac{(2eN_{a}\varepsilon_{s})^{1/2}}{C_{ox}} (V_{Dsat} + 2\phi_{Fi})^{1/2}$$

(2.29)

La tension de saturation correspondante est donnée par :

$$V_{Dsat} = V_G - 2\phi_{Fi} + \frac{2N_a \varepsilon_s}{C_{ox}^2} \left( 1 - \left( 1 + \frac{2C_{ox}^2}{2N_a \varepsilon_s} V_G \right)^{\frac{1}{2}} \right)$$

(2.30)

On obtient alors l'expression du courant de saturation en portant cette valeur de  $V_D=V_{Dsat}$  dans l'expression (2.20).

On simplifier considérablement les expressions précédentes dans le cas réaliste où le semiconducteur est peu dopé et la couche d'oxyde très mince. Dans ces conditions  $N_a$  est petit et  $C_{ox}$  est grand, de sorte que la tension de seuil du transistor (2.26), la tension de saturation (2.30) et le courant de saturation s'écrivent simplement sous la forme :

$$V_T \approx 2\phi_{Fi} \tag{2.31}$$

$$V_{Dsat} \approx V_G - 2\phi_{Fi} \approx V_G - V_T \tag{2.32}$$

$$I_{Dsat} \approx \frac{Z\mu C_{ox}}{2L} (V_G - 2\phi_{Fi})^2 \approx \frac{K_p}{2} (V_G - V_T)^2 \approx \frac{K_p}{2} V_{Dsat}^2$$

(2.33)

# II.4 Transconductance gm et conductance gd

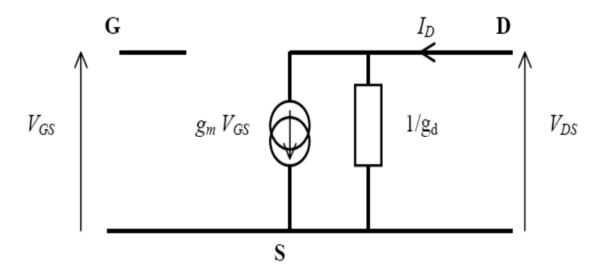

Le transistor à effet de champ à grille isolée est représenté par un schéma électrique équivalent petit signaux simplifier Figure (II.4). Les éléments principaux du schéma équivalent petit signal : la transconductance g<sub>m</sub> et la conductance de sortie g<sub>d</sub>.

Figure (II.4) : Schéma électrique équivalent du MOSFET.

# II.4.1. Transconductance g<sub>m</sub>

Par définition, la transconductance ou pente du transistor, est le rapport entre la variation du courant de drain produite par une petite variation de la tension grille, à tension drain constante [22]:

$$g_m = \frac{\partial I_D}{\partial V_G}\Big|_{V_D} \tag{2.34}$$

$\triangleright$  Dans la région linéaire,  $g_m$  est obtenue à partir de l'équation (2.25) :

$$g_{m lin} = \frac{Z\mu C_{ox}}{L} V_D = K_p \tag{2.35}$$

➤ Dans la région de saturation une dérivation de l'équation (2.33) permet d'obtenir :

$$g_{m \, sat} = \frac{Z\mu C_{ox}}{L} (V_G - V_T) = K_p (V_G - V_T)$$

(2.36)

### II.4.2. Conductance g<sub>d</sub>

La conductance de sortie due à la variation du courant de drain induite par la variation de tension de drain, lorsque la tension de grille de grille est constante [22] :

$$g_d = \frac{\partial I_D}{\partial V_D}\Big|_{V_G} \tag{2.37}$$

➤ De l'équation (2.25) on trouve l'expression de la conductance dans la région linéaire :

$$g_{d lin} = \frac{Z\mu C_{ox}}{L} (V_G - V_T) = K_p (V_G - V_T)$$

(2.38)

On voit clairement que:

$$g_{d lin} = g_{m sat} = K_p (V_G - V_T)$$

(2.39)

$\succ$  La conductance du canal dans la région de saturation est parfaitement nulle, le courant  $I_{Dsat}$  ne dépend pas de la tension  $V_D$ :

$$g_{d \text{ sat}} = 0 \tag{2.40}$$

# II.5 Effet des résistances parasites

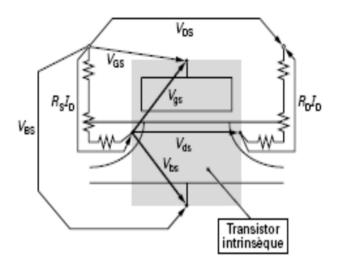

Les résistances parasites se composent de résistances d'interconnexions, de résistances de contacts et de résistances série des diffusions source et drain. Soit R<sub>S</sub> et R<sub>D</sub> respectivement le total des résistances de côté source et drain ; on a [4] :

$$R_T = R_S + R_D \tag{2.41}$$

Les chutes de tension sur ces résistances diminuent les tensions effectivement appliquées aux bornes du canal, diminuant ainsi le courant du transistor.

La figure (II.5) présente l'impact des résistances parasites sur les polarisations du TMOS (les résistances parasites de la grille et du substrat sont toujours négligées dans le bilan ; cela est justifié tant que les courants de grille et de substrat sont négligeables).

Les tensions effectivement appliquées  $(V_g,\,V_d)$  du transistor intrinsèque sont plus faibles que les tensions extérieures  $(V_G,\,V_D)$ :

$$\begin{cases} I_d = I_D \\ V_g = V_G - R_S I_D \\ V_d = V_D - R_T I_D \end{cases}$$

(2.42)

Figure (II.5) : impact des résistances parasites sur les polarisations du TMOS.

On peut déduire la caractéristique interne  $I_d$  ( $V_d$ ,  $V_g$ ) de la caractéristique externe  $I_D$  ( $V_D$ ,  $V_G$ ) en incluant l'effet des résistances d'accès de source  $R_S$  et de drain  $R_D$ .

Les expressions des courants se réécrivent de nouveau comme suit :

# • l'équation générale :

$$I_{d} = K_{p} \left( \left( V_{g} - 2\phi_{Fi} \right) V_{d} - \frac{V_{d}^{2}}{2} - \frac{2}{3} \frac{\left( 2eN_{a}\varepsilon_{S} \right)^{\frac{1}{2}}}{C_{ox}} \left( 2\phi_{Fi} \right)^{\frac{3}{2}} \left( \left( 1 + \frac{V_{d}}{2\phi_{Fi}} \right)^{\frac{3}{2}} - 1 \right) \right)$$

$$(2.43)$$

Donc:

$$I_{D} = K_{p} \left( (V_{G} - R_{S}I_{D} - 2\phi_{Fi})(V_{D} - (R_{S} + R_{D})I_{D}) - \frac{(V_{D} - (R_{S} + R_{D})I_{D})^{2}}{2} - \frac{2}{3} \frac{(2eN_{a}\varepsilon_{S})^{\frac{1}{2}}}{C_{ox}} (2\phi_{Fi})^{\frac{3}{2}} \left( 1 + \frac{(V_{D} - (R_{S} + R_{D})I_{D})}{2\phi_{Fi}} \right)^{\frac{3}{2}} - 1 \right)$$

(2.44)

### • régime linéaire :

$$I_d = K_p \left( V_g - V_T - \frac{V_d}{2} \right) V_d \tag{2.45}$$

Donc:

$$I_{D} = K_{p} \left( V_{G} - R_{S} I_{D} - V_{T} - \frac{\left( V_{D} - \left( R_{S} + R_{D} \right) I_{D} \right)}{2} \right) \left( V_{D} - \left( R_{S} + R_{D} \right) I_{D} \right)$$

(2.46)

### régime saturé :

$$I_{dsat} = \frac{K_p}{2} (V_g - V_T)^2$$

(2.47)

$$I_{Dsat} = \frac{K_p}{2} (V_G - R_S I_D - V_T)^2$$

(2.48)

La prise en compte des réductions de tensions conduites à des calculs implicites, itératifs, indésirables du point de vue de la vitesse de calcul.

### II.6 Effet de la mobilité

La mobilité des porteurs est une grandeur physique définie comme étant le coefficient de proportionnalité entre la vitesse des porteurs et le champ électrique. Elle dépend de manière complexe de la nature et de la fréquence des collisions et interactions que subissent les porteurs durant leur déplacement dans le cristal.

A l'état passant, les mobilités sont des paramètres extrêmement importants dans les transistors MOS, car elles ont une influence de premier ordre sur les valeurs du courant de drain, par conséquent, de la résistance à l'état passant [23].

Nous avons étudié le fonctionnement du transistor, en idéalisant la structure à partir de certaines hypothèses. Nous avons en particulier supposé que la mobilité des porteurs libres dans le canal conducteur est constante. Cette hypothèse, justifiée au premier ordre, devient moins justifiée dans le cas du transistor à canal court dans la mesure où le champ longitudinal devient important. Les porteurs dans le canal sont alors caractérisés par une mobilité variable qui varie avec la tension grille-source.

Cependant, il n'existe pas une loi qui traduit correctement les variations de cette mobilité et plusieurs expressions analytiques approchées été proposées. Notre choix s'est porté sur les lois suivantes:

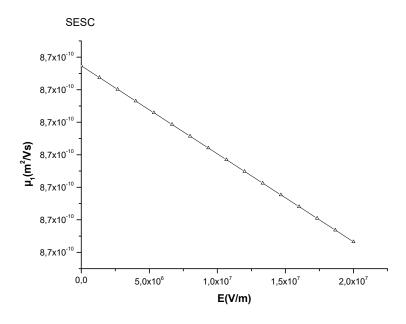

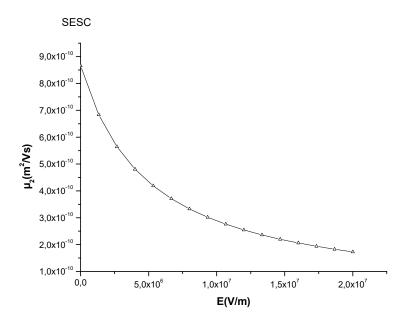

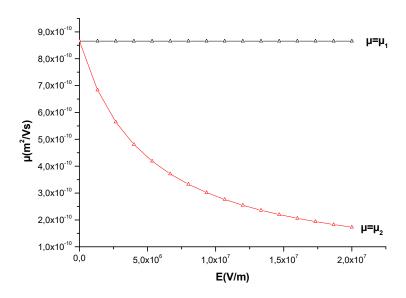

$$\begin{cases}

\mu_{1} = \frac{\mu_{0}}{1 + \theta(V_{G} - V_{T}) + E/E_{c}} & [12] \\

\mu_{2} = \frac{\mu_{0}}{[1 + \theta(V_{G} - V_{T})] + E/E_{c}} & [4]

\end{cases}$$

(2.49)

$$\mu_{2} = \frac{\mu_{0}}{\left[1 + \theta(V_{G} - V_{T})\right]\left[1 + \frac{E}{E_{c}}\right]}$$

[4]

### Avec:

μ<sub>0</sub> la mobilité des porteurs à faible champ, θ et E<sub>c</sub> (champ critique) sont deux paramètres empiriques mesurés expérimentalement (θ[V<sup>-1</sup>]=1.5/d, E<sub>c</sub> est de l'ordre 5 10<sup>4</sup>v/cm).

Le terme E/E<sub>c</sub> traduit la diminution de mobilité correspondant à la saturation de la vitesse de dérive des porteurs à fort champ longitudinal.

Le terme θ(V<sub>G</sub>-V<sub>T</sub>) traduit la variation de la mobilité associée à l'effet du champ transversal.

Dans le domaine des champs électriques faibles, les porteurs libres sont en équilibre thermodynamique avec le réseau et leur vitesse moyenne est proportionnelle au champ électrique :

$$V(E) = \mu_0 E. (2.51)$$

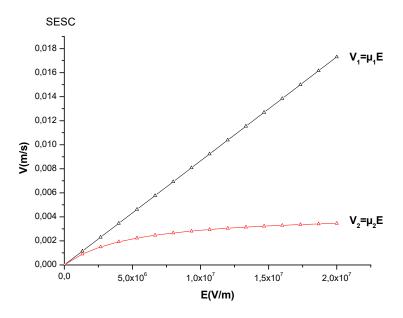

Les lois de vitesse correspondantes à  $\mu_1$  et  $\mu_2$  sont :

$$\begin{cases} v_1(E) = \mu_1(E)E = \frac{\mu_0 E}{1 + \theta(V_G - V_T) + \frac{E}{E_c}} \\ v_2(E) = \mu_2(E)E = \frac{\mu_0 E}{\left[1 + \theta(V_G - V_T)\right] \left[1 + \frac{E}{E_c}\right]} \end{cases}$$

(2.52)

$$v_2(E) = \mu_2(E)E = \frac{\mu_0 E}{\left[1 + \theta \left(V_G - V_T\right)\right] \left[1 + \frac{E}{E_c}\right]}$$

(2.53)

En reportant successivement ces lois de mobilité dans les équations (2.20), (2.27) et (2.33), nous obtenons:

#### Première loi:

#### Equation générale

$$I_{D} = \frac{Z\mu_{0}C_{ox}}{L\left(1 + \theta(V_{G} - V_{T}) + \frac{E}{E_{c}}\right)} \begin{pmatrix} \left(V_{G} - \frac{V_{D}}{2} - 2\phi_{Fi}\right)V_{D} \\ -\frac{2}{3}\frac{(2eN_{a}\varepsilon_{S})^{\frac{1}{2}}}{C_{ox}}\left(\left(V_{D} + 2\phi_{Fi}\right)^{\frac{3}{2}} - \left(2\phi_{Fi}\right)^{\frac{3}{2}}\right) \end{pmatrix}$$

(2.54)

### Régime linéaire

$$I_{D} = \frac{Z\mu_{0}C_{ox}}{L\left(1 + \theta(V_{G} - V_{T}) + \frac{E}{E_{c}}\right)} (V_{G} - V_{T})V_{D}$$

(2.55)

### • Régime saturé

$$I_{Dsat} = \frac{Z\mu_0 C_{ox}}{L \left(1 + \theta (V_G - V_T) + \frac{E}{E_c}\right)} (V_G - V_T)^2$$

(2.56)

### Deuxième loi:

### • Equation générale

$$I_{D} = \frac{Z\mu_{0}C_{ox}}{L\left[1 + \theta(V_{G} - V_{T})\right]\left[1 + \frac{E}{E_{c}}\right]} \begin{pmatrix} \left(V_{G} - \frac{V_{D}}{2} - 2\phi_{Fi}\right)V_{D} \\ -\frac{2}{3}\frac{(2eN_{a}\varepsilon_{S})^{\frac{1}{2}}}{C_{ox}}\left(\left(V_{D} + 2\phi_{Fi}\right)^{\frac{3}{2}} - (2\phi_{Fi})^{\frac{3}{2}}\right) \end{pmatrix}$$

(2.57)

### • Régime linéaire

$$I_{D} = \frac{Z\mu_{0}C_{ox}}{L[1 + \theta(V_{G} - V_{T})][1 + \frac{E}{E_{c}}]} (V_{G} - V_{T})V_{D}$$

(2.58)

### • Régime saturé

$$I_{Dsat} = \frac{Z\mu_0 C_{ox}}{L[1 + \theta(V_G - V_T)] \left[1 + \frac{E}{E_c}\right]} (V_G - V_T)^2$$

(2.59)

# II.7 Effet de la température

Les aspect thermiques dans la conception des circuits de puissance méritent souvent autant d'attention que les aspects purement électriques, car la température de fonctionnement des composants a une influence directe sur leurs caractéristiques statiques et dynamiques.

Le mode d'évolution avec la température des paramètres physiques des transistors MOS [24, 25], est déduit par des expressions analytiques applicable aux transistors MOS.

### II.7.1 Paramètres thermiques

Les caractéristiques du transistor MOS sont très sensibles à la température. Cependant la majorité des simulations supposent que la température du composant est constante, usuellement égale à la température ambiante (300°k). Un modèle thermique rigoureux exige la résolution de l'équation d'échauffement suivante :

$$C_R \rho_R \frac{\partial T_R}{\partial t} = \nabla (K_R \nabla T_R) + H_S \tag{2.60}$$

Où:

C<sub>R</sub>: chaleur spécifique du réseau.

ρ<sub>R</sub> : densité du réseau.

T<sub>R</sub>: température du réseau.

K<sub>R</sub> : conductivité thermique du réseau.

Hs: génération thermique du réseau.

La dépendance de la mobilité des porteurs en fonction de la température joue un rôle fondamental dans la détermination du courant. Une loi simple pour modéliser la variation de la mobilité avec la température est la suivante [26, 27, 28] :

$$\mu(T) = \mu(T_0) \left[ \frac{T}{T_0} \right]^{-k} \tag{2.61}$$

Avec:

T= T<sub>R</sub>: température du réseau.

$T_0 = 300$ °k : température ambiante.

K: facteur compris 2.2 à 2.7.

La variation de la vitesse de saturation avec la température pour le MOSFET est donnée par [29] :

$$V_{Sat} = \frac{2.410^5}{1 + 0.8 \exp\left[\frac{T}{600}\right]}$$

(2.62)

A température ambiante, la vitesse de saturation des électrons vaut :  $V_{sat}=10^7 \text{cm/S}$ .

Pour les trous, on a :  $V_{sat}=8.10^6$ cm/S.

Au niveau de la charge, l'augmentation de la température induit une baisse de la tension de seuil.

Une variation linéaire de V<sub>T</sub> avec la température T est suffisante pour modéliser cet effet [30, 31, 32]:

$$V_T(T) = V_T(T_0) [1 - \gamma (T - T_0)]$$

(2.63)

Où : γ est un coefficient empirique proche de 2à 3 mv/k.

# II.7.2 Dissipation thermique

La circulation d'un courant dans le semi-conducteur provoque un échauffement par effet Joule. A l'équilibre, la quantité de chaleur reçue est égale à celle dissipée à travers le boîtier dans l'air ambiant et le semi-conducteur atteint alors une température d'équilibre. Cette température ne devra pas dépasser une valeur limite  $T_{jmax}$ , sous peine de perturber les performances du dispositif, de réduire sa fiabilité ou plus grave encore de le détruire. Cette température ne devra pas excéder 175°C. En générale, on la spécifie à 150°C et parfois même à 125°C. Plus elle est basse, meilleure est la fiabilité du dispositif en fonctionnement [33].

Par analogie avec la loi d'Ohm, on écrit une équation linéaire reliant l'écart de température à la puissance dissipée, de la forme [33] :

$$T_i - T_a = R_{thia} P_d \tag{2.64}$$

Avec:

T<sub>j</sub>: Température de la jonction.

T<sub>a</sub>: Température ambiante.

R<sub>thja</sub>: Résistance thermique jonction-ambiante.

P<sub>d</sub>: Puissance dissipée.

On décompose, généralement, la résistance thermique en trois termes [33] :

$$R_{thia} = R_{thic} + R_{thcs} + R_{thsa}$$

(2.65)

Avec:

R<sub>thjc</sub>: Résistance thermique jonction-boîtier.

R<sub>thcs</sub>: Résistance thermique boîtier-dissipateur.

R<sub>thsa</sub>: Résistance thermique dissipateur–ambiante.

### Ordre de grandeur:

$R_{thjc} = 0.5$  à 3°C/W pour un transistor de puissance

R<sub>thic</sub> =100 à 500 °C/W pour un transistor de faible puissance.

$R_{thes} = 0.1 \text{ à } 0.5 \text{ °C/W}.$

$R_{thsa} = 0.5 \text{ à } 0 \text{ °C/W}.$

# **CHAPITRE III**

# Propriétés Dynamiques du MOSFET

### **III.1 Introduction**

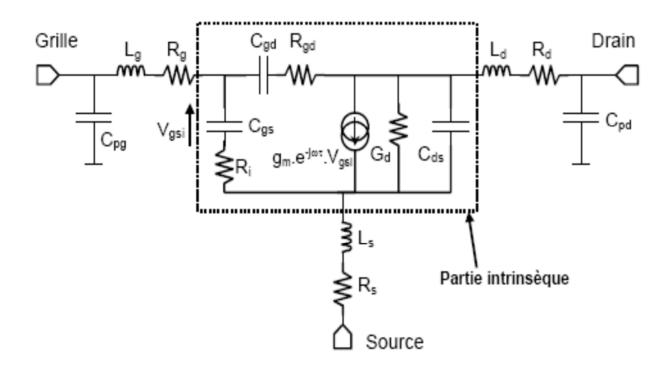

La course vers la miniaturisation des transistors MOS conduit à l'apparition des nouveaux effets ; plus précisément, certains effets jusqu'alors négligeables doivent maintenant être pris en compte. L'étude des propriétés dynamiques constitue un atout majeur dans l'application des MOSFET, et surtout pour l'adaptation de ces transistors au niveau des composants électroniques.

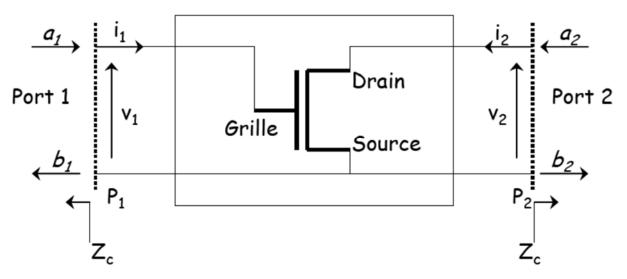

Parmi les nouveaux phénomènes à prendre en compte, deux types sont à distinguer : d'une part, il y a les effets liés au fonctionnement propre du transistor, dits effets intrinsèques, et d'autre part les effets extrinsèques, liés à l'impact résistif et capacitif de l'environnement du transistor. L'analyse d'un schéma équivalent est nécessaire pour d'écrire le comportement dynamique du TMOS.

# III.2 Schéma équivalent électrique du transistor MOSFET