## REPUBLIQUE ALGERIENNE DEMOCRATIQUE ET POPULAIRE MINISTERE DE L'ENSEIGNEMENT SUPERIEUR ET DE LA RECHERCHE SCIENTIFIQUE

# UNIVERSITE DE CONSTANTINE FACULTE DES SCIENCES DE L'INGENIEUR DEPARTEMENT D'ELECTRONIQUE

#### **THESE**

Présentée pour l'obtention du diplôme

# DOCTORAT EN SCIENCES EN ELECTRONIQUE

**Option: Composants Electroniques**

### Par TOUIDJEN Nour El Houda épouse KHENIENE

#### **THEME**

# Modélisation du Transistor à Effet de Champ (TEC) en Couches Minces à base de Silicium Polycristallin Si-L.P.C.V.D

Soutenu le : 04 /07 / 2010 devant le jury

| Mme.S.LASSOUED  | Professeur | Université de Constantine | Présidente   |

|-----------------|------------|---------------------------|--------------|

| Mme.F.MANSOUR   | Professeur | Université de Constantine | Rapporteur   |

| Mme.T.BOUCHEMAT | Professeur | Université de Constantine | Examinatrice |

| M. A.BENHAYA    | Professeur | Université de Batna       | Examinateur  |

| M. R.MAHAMDI    | Professeur | Université de Batna       | Examinateur  |

| M.M.S. AIDA     | Professeur | Université de Constantine | Invité       |

# Remerciements

Le travail que nous présentons dans ce mémoire a été effectué au sein du Laboratoire d'Etude des Matériaux Electroniques pour Application Médicale (LEMEA MED) du département d'Electronique de Constantine.

Nous tenons à remercier très vivement les membres qui nous ont fait l'honneur d'accepter de participer au jury de notre soutenance de thèse :

Mme S.LASSOUED, Professeur au département d'Electronique, Université de Constantine, pour avoir bien voulu juger nos travaux et l'honneur qu'elle nous a accordé en acceptant la présidence de notre commission d'examen.

Mme F.MANSOUR, Professeur au département d'Electronique, Université de Constantine, pour la confiance qu'elle m'a témoignée en acceptant la direction de ma thèse, pour avoir suivi de très près mon travail et m'avoir fait bénéficier de sa compétence et de ses connaissances multidisciplinaires.

Mme T.BOUCHEMAT, Professeur au département d'Electronique, Université de Constantine, pour l'attention qu'elle a portée à ce mémoire et l'honneur qu'elle nous a fait en siégeant au jury de soutenance.

M. A.BENHAYA, Professeur à l'Université de Batna, pour avoir accepté de participer au jury de notre thèse et pour la caution scientifique qu'il veut bien apporter à nos travaux.

M. R.MAHAMDI, Professeur à l'Université de Batna, pour l'intérêt qu'il a porté à nos travaux de thèse et pour avoir accepté de les juger en tant qu'examinateur.

Nous tenons également à exprimer notre profonde reconnaissance à M.S. AIDA, Professeur au département de physique, Université de Constantine, pour ses précieux conseils.

Gratitude et reconnaissance vont également à M.BELLEL, Professeur au département d'Electronique, Université de Constantine et M.N.MERABTINE, Professeur au département d'Electronique, Université de Constantine.

Enfin que tous ceux qui par leur enseignements, leurs encouragements et leur amitié, trouvent ici l'expression de ma profonde gratitude.

# Sommaire

| INTRODUCTION GENERALE                                                                                     | 1   |

|-----------------------------------------------------------------------------------------------------------|-----|

| Chapitre I: Evolution des technologies des Ecrans plats et des T<br>en polysilicium et leurs applications | FTs |

| INTRODUCTION                                                                                              | 5   |

| I. Techniques mises en oeuvres.                                                                           | 6   |

| II. Evolution et contexte economique                                                                      | 7   |

| III. Ecrans à cristaux liquides ou LCD (liquid crystal displays)                                          | 9   |

| III.1. Les cristaux liquides                                                                              | 10  |

| III.2. Ecrans LCD et leurs technologies mises en œuvre                                                    | 12  |

| III.2.1. Ecrans LCD à nématique en hélice ou à matrice passive                                            | 13  |

| III.2.2. Ecrans LCD à matrice active ou AMLCD                                                             | 14  |

| III.2.3. Technologies et performances requises pour les transistors en couche                             |     |

| Mince                                                                                                     | 19  |

| III.2.4. Avantages des TFTs en poly-Si dans l'application AMLCD                                           | 20  |

| IV. Descriptions physique et electrique des transistors en couche mince (TFTs) a base of                  |     |

| polysilicium                                                                                              | 21  |

| IV.1. Structure des transistors en couche mince (TFT en poly-Si)                                          | 22  |

| IV.1.1. Matériaux organique                                                                               | 23  |

| IV.1.2. Matériaux inorganique                                                                             | 24  |

| IV.2. Régimes de fonctionnement du TFT en poly-Si à basse température                                     | 29  |

| IV.3. Paramètres électriques des TFTs en poly-Si                                                          | 30  |

| IV.3. 1. Courant de fuite                                                                                 | 30  |

| IV.3. 2. Tension de seuil                                                                                 | 31  |

| IV.3.3. Pente sous le seuil                                                                               | 31  |

| IV 3.4 Mobilité des porteurs                                                                              | 32  |

| IV.3.5. Influence de la taille des grains sur les paramètres électriques du T      | FT |

|------------------------------------------------------------------------------------|----|

| poly-Si                                                                            | 32 |

| IV.4. Stabilité des paramètres électriques                                         | 33 |

| IV.5. Effet kink                                                                   | 33 |

| IV.5.1. Phénomène d'impact par ionisation                                          | 34 |

| IV.5.2. Réduction de l'effet kink et technologie LDD                               | 35 |

| V. Technologies emergentes et concurrentes                                         | 35 |

| V.1. Technologie d'écrans plats à diodes électroluminescentes organiques (OLED)    | 36 |

| V.1.1. Structure d'une OLED.                                                       | 37 |

| V.1.2. Principe de fonctionnement d'une cellule OLED                               | 38 |

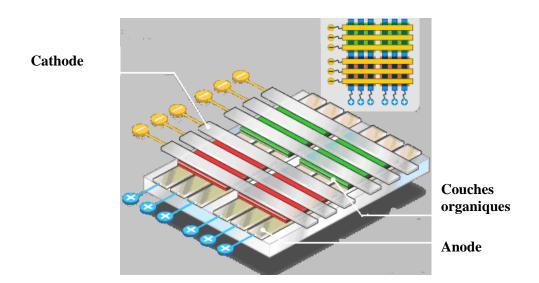

| V.2. Ecran OLED à matrice passive (PMOLED)                                         | 39 |

| V.3. Ecran OLED à Matrice active (AMOLED)                                          | 40 |

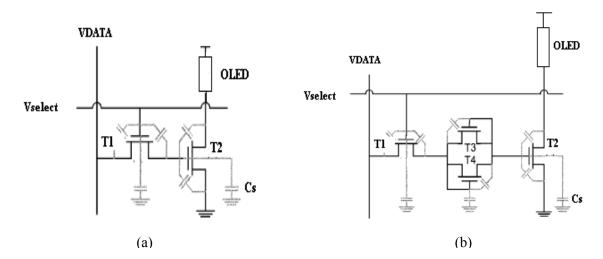

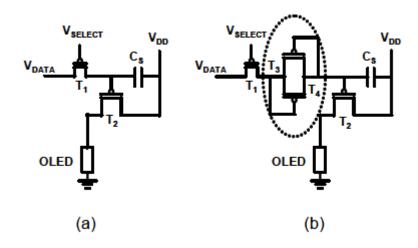

| V.3.1. Circuits d'adressages de pixels en programmation tension                    | 42 |

| V.3.2. Circuits d'adressages de pixels en programmation courant                    | 43 |

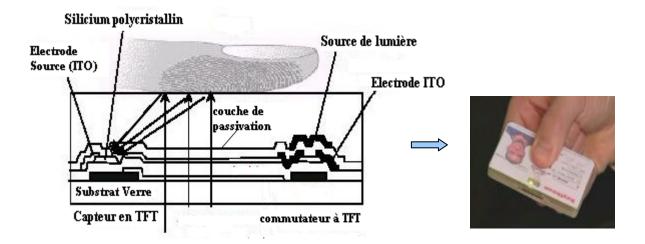

| VI. Autres applications des TFTs en polysilicium en grande surface                 | 45 |

| CONCLUSION                                                                         | 47 |

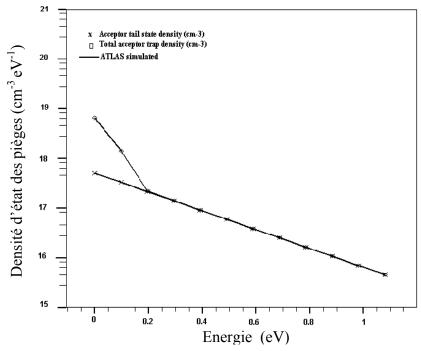

| d'Etat des Pièges dans le Polysilicium                                             |    |

| INTRODUCTION                                                                       | 50 |

| I. Structure et propriétés électriques du film du silicium polycristallin Si-LPCVD | 50 |

| I.1. Structure.                                                                    | 50 |

| I.2. Propriétés électriques du film polysilicium Si-LPCVD                          | 51 |

| I.3. Diagramme de bandes de la structure polysilicium                              | 52 |

| II. Densité d'état des porteurs de charge                                          | 54 |

| II.1. Densités des porteurs libres                                                 | 55 |

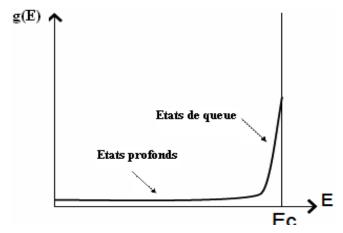

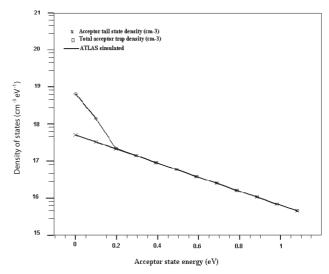

| II.1.1. Densité des porteurs localisés sur la queue de bande                       | 55 |

| II.1.2. Densité des porteurs localisés sur les centres profonds                    | 55 |

| II.2. Régime au dessous du seuil                                                   |    |

| II.3. Régime au dessus du seuil                                                    | 56 |

| č                                                                                  |    |

# Chapitre III : Modélisation Electrique du Transistor en couche mince à base de Silicium Polycristallin

| I. Présentation                                                   |                                                                                   |

|-------------------------------------------------------------------|-----------------------------------------------------------------------------------|

|                                                                   | n des principaux modèles des transistors en couche mince en polysilicium 63       |

| II. Formulati                                                     | on du modèle analytique d'un TFT en poly-Si64                                     |

|                                                                   | II.1 Choix du modèle et hypothèses considérées                                    |

|                                                                   | II.2 Mise en équation du modèle statique courant-tension                          |

|                                                                   | II.2.1. Expression générale du courant de drain                                   |

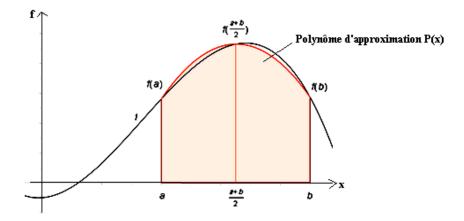

|                                                                   | II.2.2. Méthode de résolution numérique du courant de drain71                     |

|                                                                   | II.2.3. Modélisation analytique de l'effet kink                                   |

|                                                                   | II.2.4. Analyse de la mobilité d'effet de champ d'un TFT poly-Si74                |

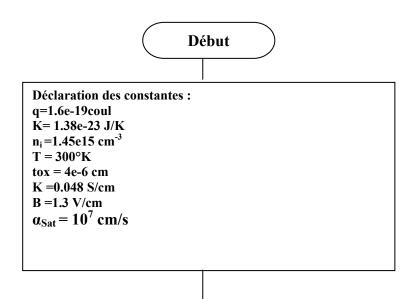

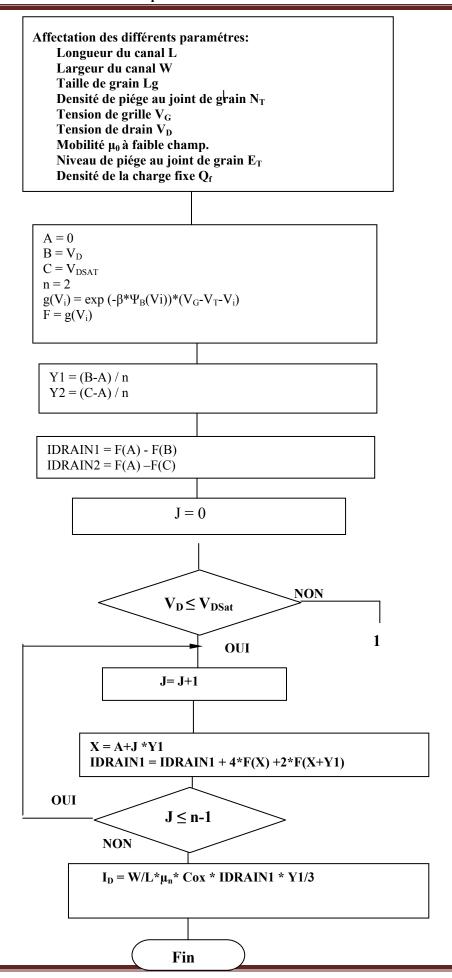

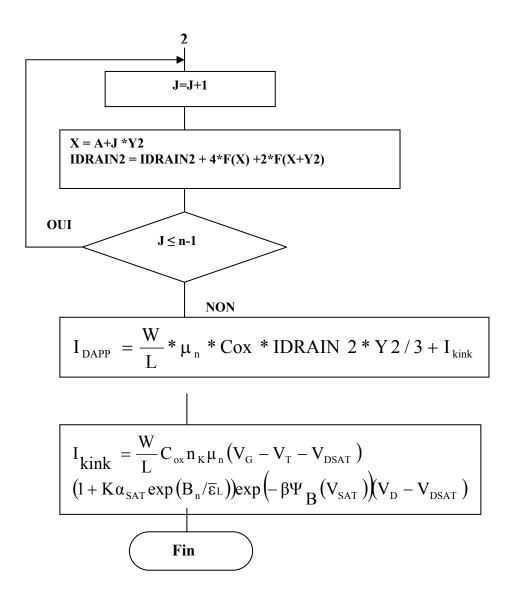

|                                                                   | II.3. Mise en œuvre du programme de simulation et organigramme76                  |

|                                                                   | II.4. Modélisation du transistor TFT poly-Si par approximation de la feuille      |

| de charge                                                         | 79                                                                                |

| CONCLUSI                                                          | ON80                                                                              |

|                                                                   |                                                                                   |

| INTRODUC                                                          | TION 83                                                                           |

| INTRODUC                                                          | TION                                                                              |

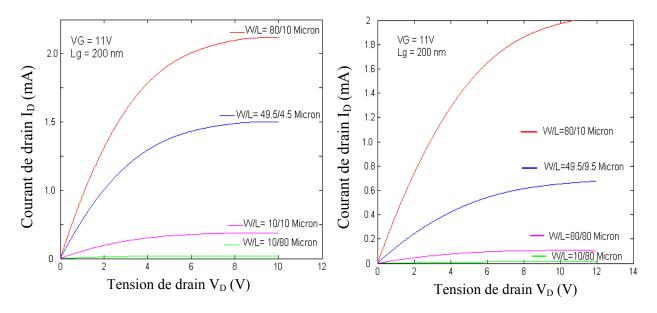

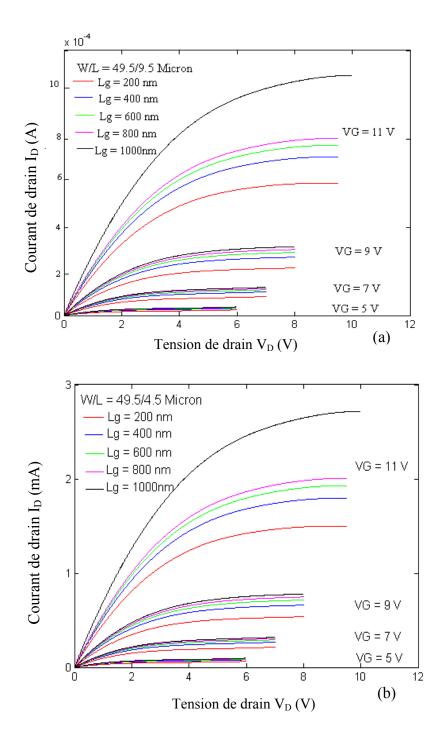

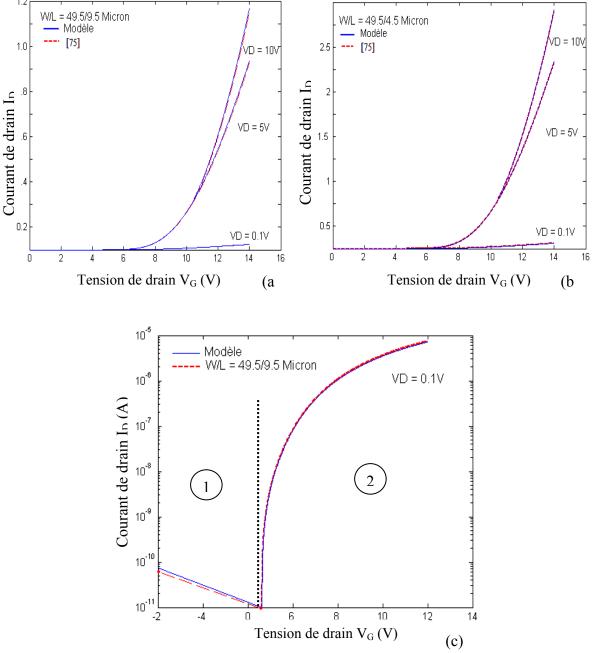

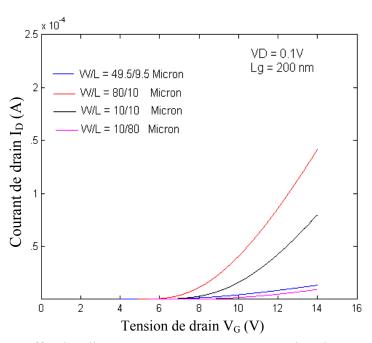

| I. Caractérist                                                    | TION                                                                              |

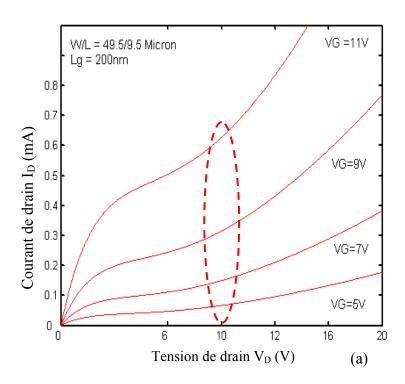

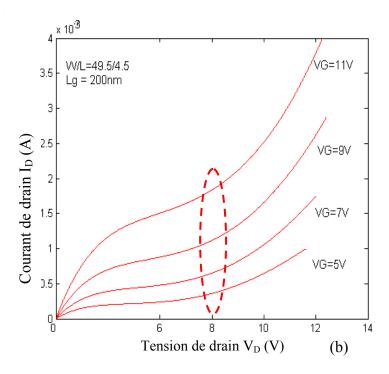

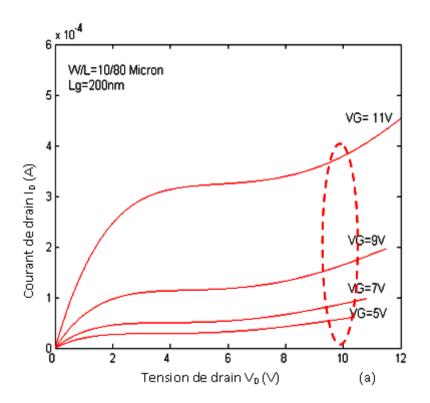

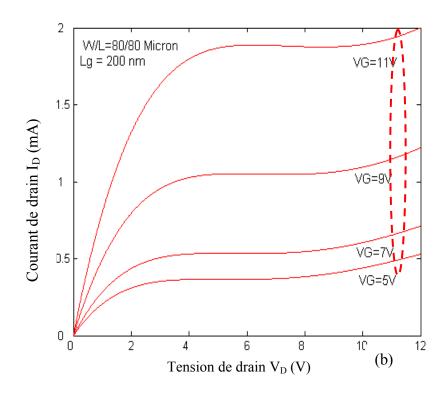

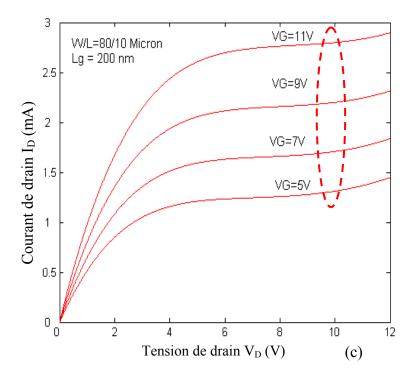

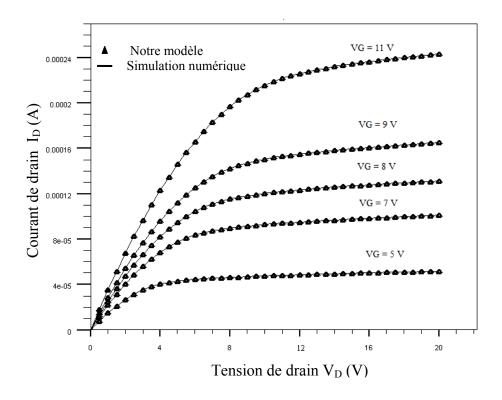

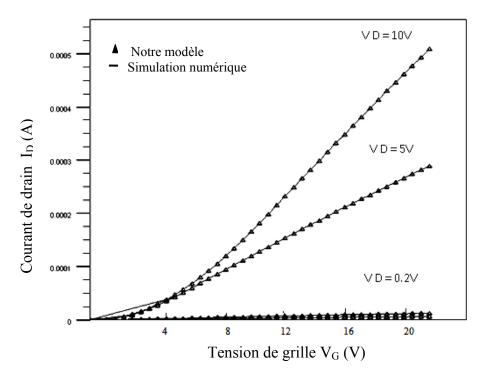

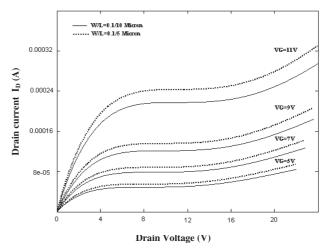

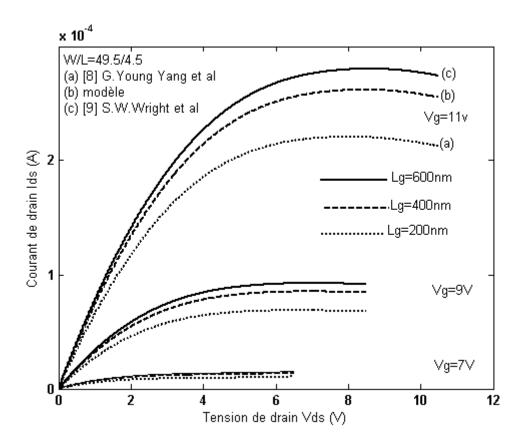

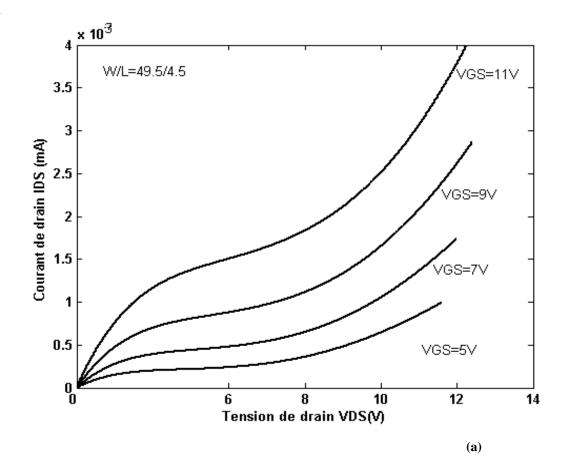

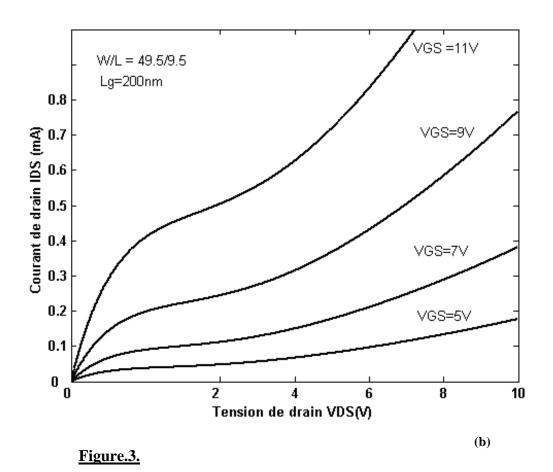

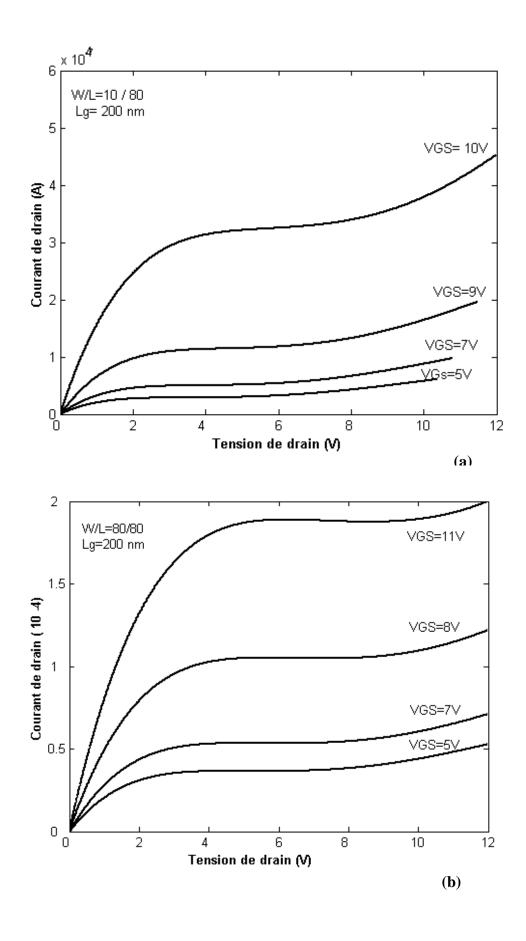

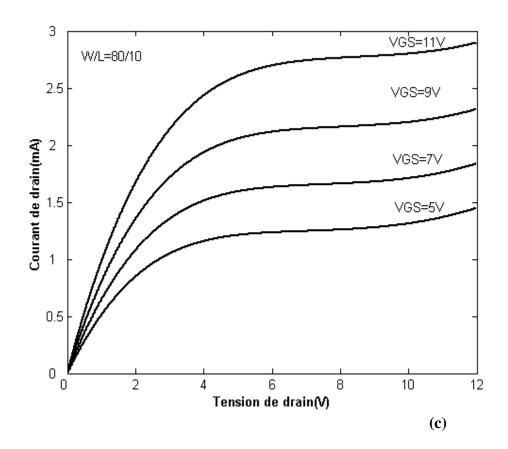

| I. Caractérist                                                    | iques électriques de sortie courant-tension d'un TFT poly-Si à canal n sans effet |

| I. Caractérist                                                    | iques électriques de sortie courant-tension d'un TFT poly-Si à canal n sans effet |

| I. Caractérist                                                    | iques électriques de sortie courant-tension d'un TFT poly-Si à canal n sans effet |

| I. Caractérist                                                    | iques électriques de sortie courant-tension d'un TFT poly-Si à canal n sans effet |

| I. Caractérist kink                                               | iques électriques de sortie courant-tension d'un TFT poly-Si à canal n sans effet |

| I. Caractérist kink                                               | iques électriques de sortie courant-tension d'un TFT poly-Si à canal n sans effet |

| I. Caractérist kink                                               | iques électriques de sortie courant-tension d'un TFT poly-Si à canal n sans effet |

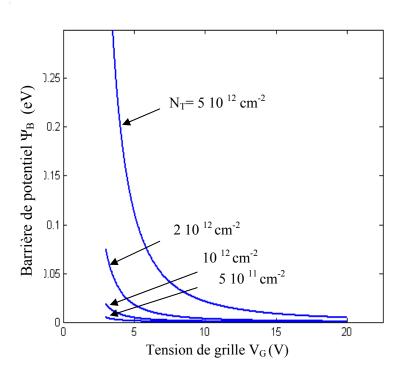

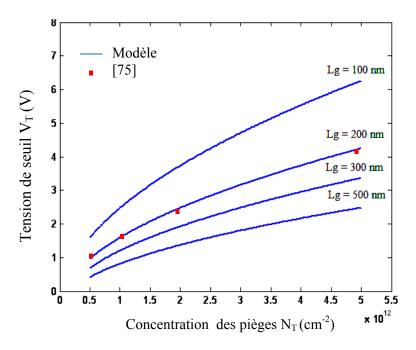

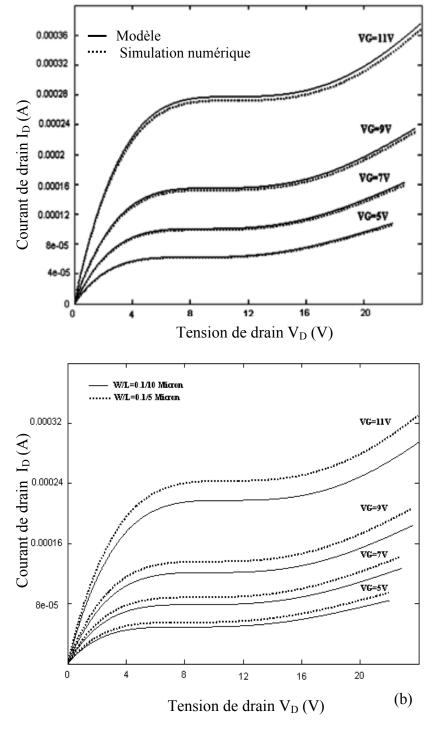

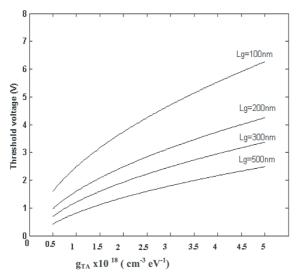

| I. Caractérist kink  II. Caractéris  III. Influence hauteur de ba | iques électriques de sortie courant-tension d'un TFT poly-Si à canal n sans effet |

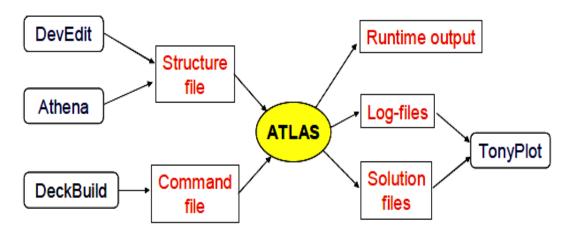

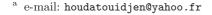

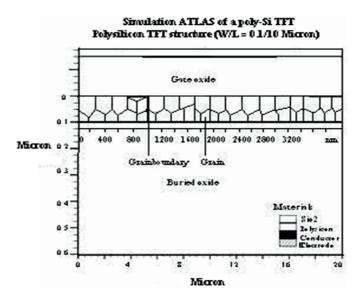

| V. Implantation du modèle dans le simulateur TCAD-ATLAS                  |

|--------------------------------------------------------------------------|

| V.1. Environnement du simulateur TCAD-ATLAS                              |

| V.2. Résultats de simulation du modèle du TFT en poly-Si sous TCAD-      |

| ATLAS                                                                    |

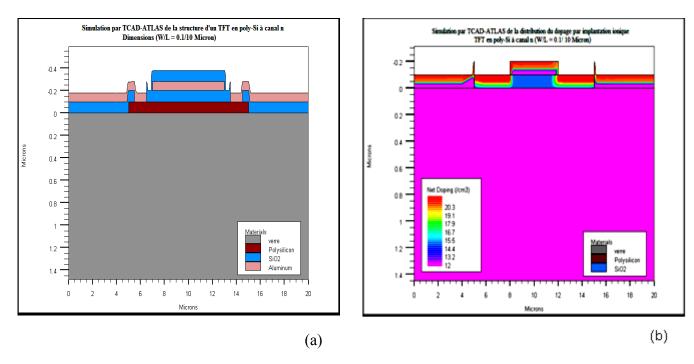

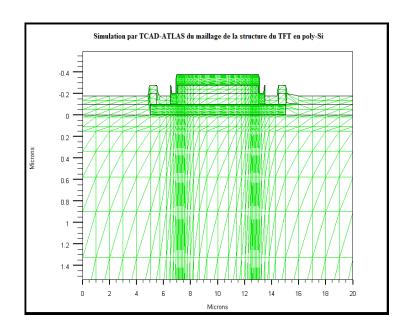

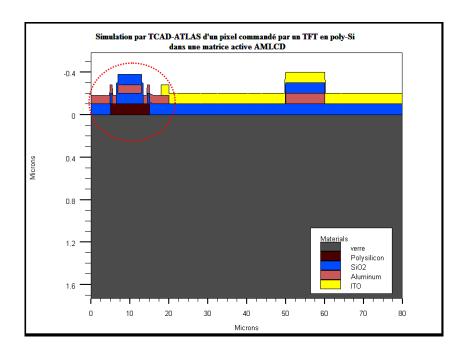

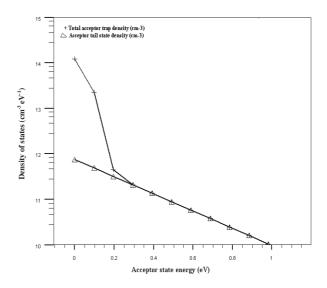

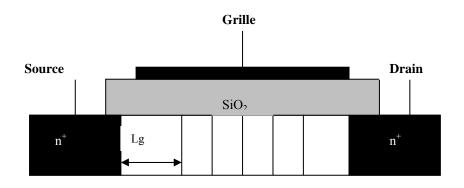

| V.2.1. Simulation de la structure bidimensionnelle du TFT en poly-Si 100 |

| V.2.2. Conditions aux limites                                            |

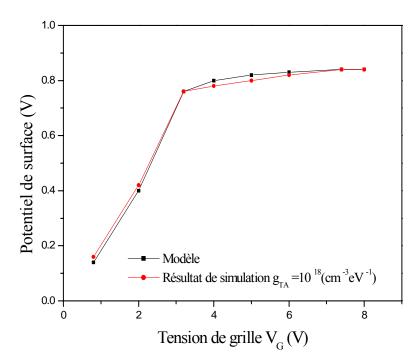

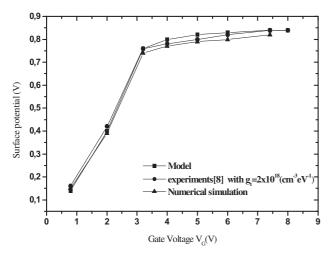

| V.2.3. Profil du potentiel de surface                                    |

| V.2.4. Caractéristiques de sortie courant-tension du TFT en poly-Si 104  |

| VI. Extraction des paramètres électriques                                |

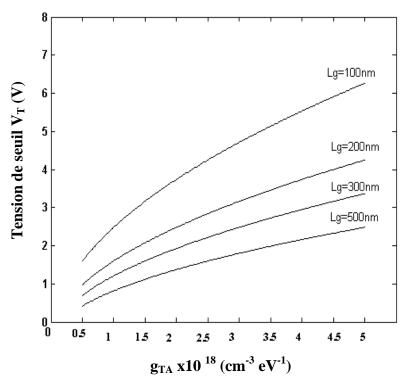

| VI.1. Tension de seuil                                                   |

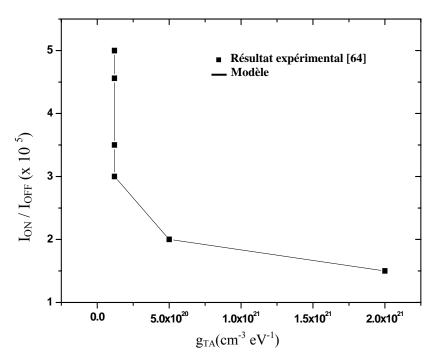

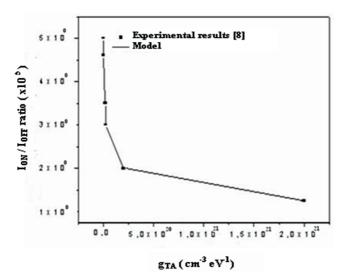

| VI.2. Rapport I <sub>ON</sub> / I <sub>OFF</sub>                         |

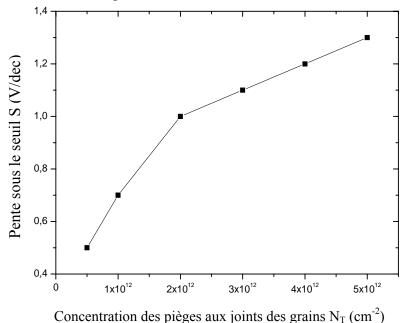

| VI.3. Pente sous le seuil                                                |

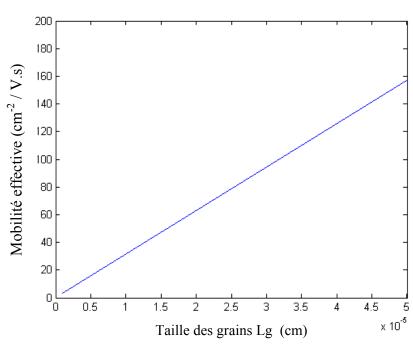

| VI.4. Mobilité d'effet de champ du TFT en poly-Si à canal n              |

| CONCLUSION114                                                            |

| CONCLUSION GENERALE 116                                                  |

| BIBLIOGRAPHIE119                                                         |

# Introduction Generale

Les transistors en couches minces à base de polysilicium, connus sous leur acronyme anglais TFTs (Thin Film Transistors) en poly-Si sont de nos jours établis comme faisant partie d'un développement de technologies à coût peu élevé pour de larges applications dans le domaine de la microélectronique. Différentes applications sont apparues suite aux possibilités qu'offre la combinaison entre le savoir-faire accumulé dans la micro électronique et les nouveaux horizons ouverts par l'utilisation de substrats de dimensions élevées. L'une des principales applications qui a trouvé un grand essor se situe dans les écrans plats à cristaux liquides et à matrice active (AMLCD) (Active Matrix Liquid Crystal Displays), et il se trouve que les transistors en couche mince à base de polysilicium sont parfaitement adaptés à une telle utilisation. En effet, ces transistors sont des dispositifs de première importance, lorsqu'il s'agit de piloter des matrices des écrans plats où ils sont appelés à remplacer les TFTs en silicium amorphe, en raison d'une durée de vie des porteurs plus importante [1,2].

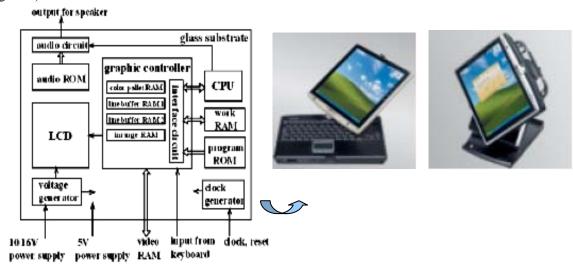

Or, l'intérêt de l'utilisation du Silicium polycristallin dans ce type de composants permet de fabriquer des écrans de grande taille. En plus, les divers TFTs en poly-Si peuvent être intégrés directement sur le substrat en verre grâce à la facilité de dépôt du polysilicium en donnant de meilleures performances électriques par rapport au Silicium amorphe (a-Si).

Le choix du polysilicium pour la réalisation du canal de ce type de transistors est lié de façon directe à leurs performances électriques, vu que dans la majorité des modèles de conduction, les propriétés de ce matériau tiennent compte d'une structure particulière à base de grains et de joints de grains [3, 4,5].

L'idée du sujet proposé dans le cadre de cette thèse de Doctorat, à caractère essentiellement théorique, porte sur l'étude analytique et la modélisation du comportement électrique d'un transistor en couche mince ou TFT (Thin Film Transistor) réalisé à base de polysilicium, où ce matériau joue le rôle de semi-conducteur actif. C'est donc dans du polysilicium que seront diffusés les zones de source et de drain, ainsi que le canal de conduction (de type P ou N selon le dopage).

Il est ainsi primordial de maîtriser les propriétés électriques de ce semi-conducteur, particulièrement la mobilité des porteurs du canal, avant d'entamer la phase d'étude analytique du comportement électrique du transistor en question.

Dans un premier chapitre, nous exposerons un état de l'art des diverses technologies actuelles et concurrentes du transistor en couche mince et ses multiples applications, allant de la technologie des cristaux liquides ou LCD (Liquide Crystal Display) à celle des diodes électroluminescentes organiques ou OLD (Organic Light-Emitting Diode), jusqu'à la technique des écrans systèmes SOG (System On Glass).

Nous présenterons, éventuellement une étude physique et électrique du TFT réalisé à base de polysilicium, qui constitue l'élément essentiel (ou pixel) de commutation et de commande des circuits d'adressage des matrices actives AMLCD (Active Matrix Liquid Crystal Display) et AMOLED (Active Matrix Organic Light-Emitting Diode). L'historique de ces matrices, leur principe ainsi que leur mode de fonctionnement seront étudiés en détail.

Sachant que le polysilicium est le matériau de base pour la fabrication du transistor en question, une étude descriptive de sa structure cristalline ainsi que de son mode de dépôt fera l'objet de ce chapitre introductif.

Dans le second chapitre, nous traiterons les propriétés de transport et la distribution de la densité des pièges dans le polysilicium afin de pouvoir dégager des hypothèses qui peuvent mener à un modèle analytique simplifié du transistor dans ses différents régimes de fonctionnement, plus particulièrement les régimes au dessous du seuil et au dessus du seuil. Nous présenterons, également les différents types de charges et leur contribution à la densité des porteurs localisés sur les queues de bandes et sur les centres profonds au niveau des joints de grains. Nous traiterons aussi de la variation du potentiel électrostatique dans la structure.

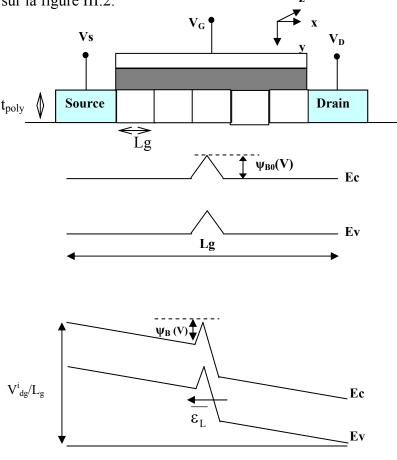

Le troisième chapitre sera consacré à la modélisation du comportement électrique du transistor TFT en poly-Si. Le modèle ainsi élaboré visera à relier la mobilité des porteurs et la hauteur de barrière de potentiel à la densité de pièges présente aux joints de grains et à la tension de grille appliquée.

Des démarches moyennant quelques approximations nous permettrons d'aboutir aux expressions du courant de drain, que nous comparerons avec celles déjà publiées. Ainsi, elles nous faciliteront l'introduction d'un nouvel aspect de modélisation.

Ce même modèle tiendra compte de certains effets nocifs pouvant dégrader les caractéristiques électriques du TFT poly-Si, en y apportant une amélioration.

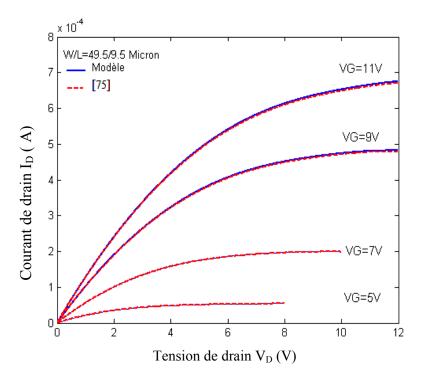

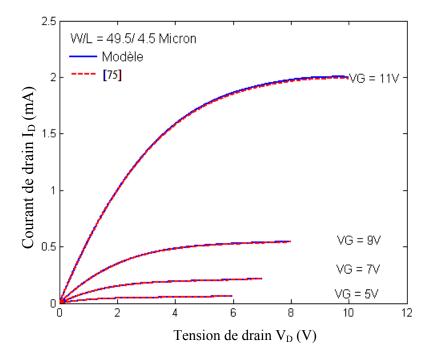

Le quatrième chapitre englobera l'ensemble des tracés théoriques illustrant l'évolution des caractéristiques de transfert courant-tension pour diverses valeurs de tensions de sortie, en considérant l'effet de la variation des dimensions du canal, de la taille des grains, de la tension de seuil, et de la hauteur de barrière d'énergie aux joints de grains.

La validité du modèle sera montrée en confrontant les différents tracés cités auparavant avec des résultats expérimentaux et théoriques issus de la littérature.

Dans la même optique, il sera judicieux de développer, en parallèle, un savoir faire par rapport à un logiciel de simulation de composants électroniques récemment acquis par notre laboratoire, à savoir le TCAD-ATLAS (SILVACO), ce qui pourra être bénéfique, d'une part pour permettre d'affiner et préciser le modèle élaboré pour de nouvelles technologies, et d'autre part pour apporter un complément scientifique au travail consacré dans cette étude.

A la fin de ce mémoire, nous présentons une conclusion générale qui englobera l'ensemble des résultats et discussions de la modélisation électrique du TFT à base de polysilium.

# Chapitre 1

Evolution des technologies des écrans plats et des TFTs à base de polysilicium et leurs applications

#### **INTRODUCTION:**

Depuis l'apparition des écrans, le marché de l'affichage a été largement dominé par les écrans à tube cathodique ou CRT (Cathode Ray Tube) souvent présents dans l'environnement informatique et grand public.

La technologie de ce type d'écran, qui avait atteint son apogée en terme de qualité et de coût, souffrait d'un certain nombre de limitations telles que l'encombrement, le poids et la consommation en terme d'énergie. Ces contraintes constituent alors un véritable obstacle à leur utilisation essentiellement pour les produits portables. Ainsi, les écrans CRT ont atteint des limites techno/économiques à partir de 35 à 40 pouces en vision directe [1].

Depuis ces dix dernières années, l'enjeu du développement technologique des écrans plats gagne de plus en plus en parts du marché au dépend des écrans à tube cathodique. Il s'agit d'offrir une solution aux applications pour lesquelles l'encombrement est déterminant, d'essayer de couvrir en vision directe des applications de grandes tailles supérieures à 40 pouces. Enfin, l'enjeu est de concurrencer inexorablement les anciens écrans et leurs applications majeures (moniteurs informatiques, télévision...).

Notons que les écrans plats connus sous leur acronyme anglais FPDs (Flat Panel Displays) sont des dispositifs de visualisation ou d'affichage à structure matricielle et de faible épaisseur par rapport à l'ancienne technologie dominante. Leur fonction essentielle est de pouvoir visualiser des données et des images de haute qualité sur un espace à faible encombrement (une épaisseur de l'écran de 10 cm), avec peu de chaleur dégagée, et une absence totale de scintillement de l'écran, comparés aux écrans classiques [2].

De ce fait, ces écrans jouent un rôle particulièrement stratégique au sein des équipements électroniques menus d'un système de visualisation car ils représentent une part importante dans le coût total. Aussi, ils sont susceptibles de créer de nouveaux marchés tels que les ordinateurs et les téléphones portables.

Si à leur première sortie les écrans plats furent beaucoup critiqués par leur qualité d'image moyenne (rémanence élevée, pauvreté des couleurs, angles de vision trop étroits etc...), ils représentent une révolution technologique tant sur le plan technique qu'esthétique. Ils ont connu leur première grande utilisation pour les cadrans des montres à affichage numérique, les calculatrices, ordinateurs portables, puis l'expansion s'est ensuite généralisée à tous les affichages miniaturisés sur de nombreux systèmes électroniques et à

mesure que la technologie évoluait, l'affichage a fait de plus en plus son apparition pour les écrans d'ordinateurs jusqu'aux téléviseurs grand écrans plats [3,4].

Ainsi, nous avons pour vocation dans ce chapitre introductif de présenter une étude exhaustive des techniques mises en œuvre pour la fabrication des écrans plats. Le sujet étant vaste et évoluant beaucoup trop rapidement, il va falloir regrouper les technologies majeures utilisées.

Or, dans un écran plat et plus particulièrement à matrice active, le transistor en couche mince joue le rôle de commutateur entre la phase d'adressage et de maintien. Notons que le silicium polycristallin constitue la couche active où seront diffusés les zones de source, de drain, et du canal de conduction (de type P ou N) du transistor. Un rappel théorique sera consacré aux propriétés physiques et électriques du polysilicium, puis une description de la structure et du fonctionnement du transistor en couche mince à base de ce matériau sera présentée où une analyse détaillée traitera l'influence de ces propriétés sur les paramètres électriques (tension de seuil, pente sous le seuil, mobilités des porteurs...). Nous examinerons également, l'évolution des principales applications de ce transistor en particulier dans les écrans plats puis dans d'autres domaines que le monde de la visualisation.

Enfin, cet état de l'art des technologies du transistor en couche mince à base de polysilicium nous permettra d'introduire la problématique et les objectifs fixés dans le cadre de cette étude.

#### I. Techniques de mise en œuvre :

Il existe de nombreuses technologies d'écrans plats dont les principales sont :

- Ecrans à cristaux liquides ou LCD (Liquid Crystal Display) qui permettent la réalisation non seulement des écrans plats à vision directe, mais aussi une projection d'images de grande taille. D'où des applications plus performantes des écrans à cristaux liquides et à matrice active ou TFT (Thin Film Transistors) par rapport à ceux à matrices passives de type TN (Twisted Nematic) ou STN (Super Twisted Nematic) [5] etc...

- Ecrans utilisant des technologies émissives telles que : les écrans à plasma ou PDP  $\triangleright$ (Plasma Display Panel), les écrans électroluminescents OLED (Organic Light Emitting Displays) [6,7].

Ecrans utilisant d'autre technologies tels que : Ecrans à micro-miroirs ou DMD (Digital Micromirror Device).

A ce jour, seuls les dispositifs à cristaux liquides, à plasma et électroluminescents font l'objet d'une industrialisation de masse, d'autant plus que les écrans de type LCD constituent de loin le segment le plus important de l'industrie des écrans plats (87% à 95%) [8,9].

#### II. Evolution et contexte économique :

Selon la société d'étude Display Search, le marché global de vente a atteint plus 10,8 millions de télévisions LCD (TV LCD) pour seulement 2,3 millions de téléviseurs à Plasma (TV à plasma) en 2006 ; soit une progression de 99% pour la technologie LCD et 45% pour celle à plasma durant la même période de production. Si l'on compare ces chiffres, on constate que la progression productive est de 15% pour les TV LCD et elle n'est que de 4% pour les TV à plasma. Au total, il se vend ainsi quatre fois plus d'écrans LCD que ceux à Plasma. La raison est que la technologie LCD équipe ses écrans de petites et de moyennes tailles d'environ 15 à 40 pouces, entre autre 33 centimètres à un mêtre d'où une demande croissante de ce type d'écrans plus légers et plus ergonomiques par les consommateurs plus particulièrement en Europe [10,11].

Alors que la technologie à plasma est toujours réservée pour des écrans de grande taille (plus d'un mètre en général). En terme de chiffre d'affaires, les revenus des écrans TV LCD ont atteints les 12 milliards de dollars (84% de croissance sur un an) et plus de 4,5 milliards pour les Plasma (18% de croissance sur un an). La société Display Search tient à préciser que si la croissance du chiffre d'affaires des Plasma est plus faible, c'est en partie dû à une chute des prix par an. A titre d'exemple, le prix moyen d'un écran plasma de 50 pouces (127 cm) est passé de 2000 € en 2005 à 1500 € en 2006 soit une baisse de 30% [12].

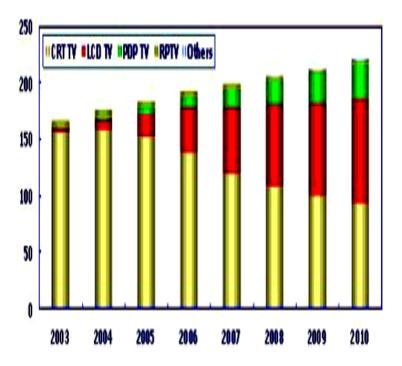

Les prévisions pour l'année 2010 estiment une production de plus de 90 millions d'unités LCD contre 25 millions d'unités PDP par année. Ces estimations sont représentées par les figures I.1 et I.2 qui montrent les parts du marché de la télévision ainsi que le pourcentage de production d'écran par technologie dans le monde entre les années 2005 à 2010 [13].

Fig.I.1 Prévisions des parts du marché de la télévision rapportées par la société Display search [12,13]

Fig.I.2 Pourcentage de production d'écran par technologie rapporté par Display search [12,13]

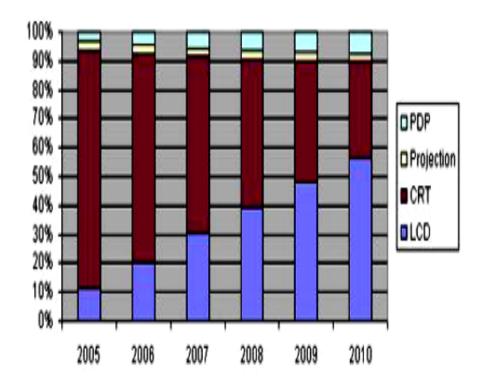

L'accessibilité au grand format d'image supérieure à 40 pouces se fait au moyen d'un système d'imagerie par projection réservée aux manifestations médiatiques ou aux salles de super vision. Actuellement, la technique dominante en rétro-projection exploite la technologie des cristaux liquides ou LCD de type TFT en polysilicium qui fera l'objet d'une étude détaillée dans ce premier chapitre (voir Fig.I.3). Cette technologie qui prétend se positionner jusqu'à une taille de 54", offre une industrie sur verre qui fonctionnera avec des dalles 2 m<sup>2</sup>

Afin de développer une telle technologie sur le marché mondial, de nouvelles techniques auront un rôle primordial à jouer comme le remplissage par goutte du cristal liquide. Ce qui a pour effet d'augmenter les cadences de production [14, 15]

PDA: Personal Digital Assistant, WS: Workstation, TV: Télévision

Fig.I.3.Différentes technologies couvrant un vaste domaine d'application [15]

#### III. Ecran à cristaux liquides ou LCD (Liquid Crystal Displays) :

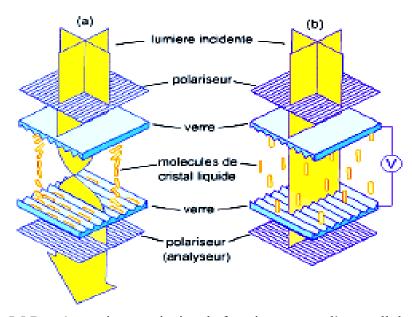

Un écran à cristaux liquides ou LCD utilise la polarisation de la lumière grâce à des filtres polarisants et à la biréfringence de certains cristaux liquides en phase intermédiaire (entre solide et liquide). D'un point de vue optique, cet écran est un dispositif passif (n'émet pas de lumière) et à transparence variable qui doit être constamment éclairé.

Il assure, donc, l'affichage d'un grand nombre de dispositifs électroniques tels que les calculatrices, les montres, les moniteurs d'ordinateurs...Actuellement, il permet de visualiser en couleur dans des dimensions dépassant le mètre en diagonale (Télévision grand public).

#### III.1. Les cristaux liquides :

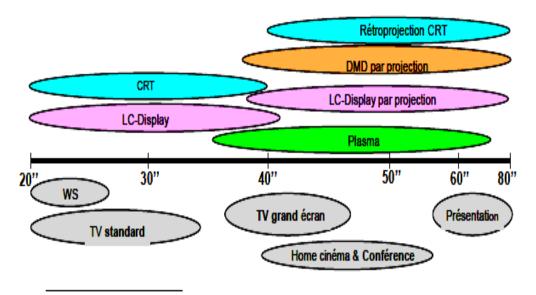

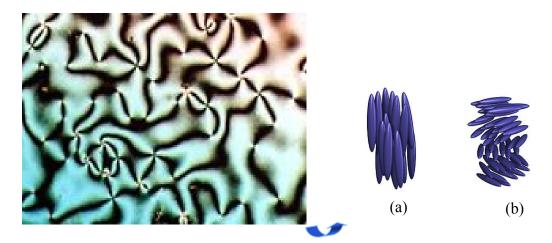

Découverts en 1877 par Otto Lehmann, les cristaux liquides sont des matières organiques à base de carbone présentant un état intermédiaire entre la phase liquide et solide ou phase nématique (voir Fig.I.4 (a)) où les molécules en forme allongée et désordonnée (comme dans un liquide), sont réparties en moyenne parallèlement les unes aux autres avec un certain ordre d'orientation (comme dans un cristal) (voir Fig.I.4 (b)).

Ces cristaux possèdent des propriétés optiques intéressantes car ils ont la possibilité de modifier la propagation (ou polarisation) de la lumière en fonction du champ électrique qu'on leur applique [16].

Un filtre polarisant, en forme de grillage dense et mince, impose aux rayons lumineux incidents de nature incohérente une direction parallèle à ses fentes [17].

Fig.I.4. Texture de la matière en phase nématique

- (a) position des molécules en phase nématique

- (b) position des molécules en phase nématique hélicoïdale [17]

En général, un écran LCD est constitué d'une couche de cristal liquide comprise entre deux plaques ou dalles en verre (Fig.I.5).

Des polariseurs transparents sont placés à l'extérieur de ces dernières qui ne laissent passer que les rayons présentant une certaine orientation.

Les rayons ainsi triés en passant à travers la couche des cristaux liquides vont se voir soit inaffectés, soit orientés suivant une direction perpendiculaire (90°) si un champ électrique est appliqué aux molécules. Un surfactant est alors déposé sur la paroi intérieure des plaques afin d'orienter ces molécules suivant la direction désirée. Au repos, les cristaux liquides tendent à s'aligner les uns sur les autres, l'orientation des molécules étant de 90°. Ils adoptent ainsi une disposition en forme d'hélice.

La lumière véhiculée par ces molécules ressort de la cellule suivant la direction du polariseur (Fig.I.5 (a)). On parlera alors d'une cellule passante (présence de lumière).

Sous l'influence d'un champ électrique, les molécules abandonnent totalement leur état hélicoïdal pour s'aligner suivant la direction du champ. La lumière, qui n'est plus déviée par les molécules, est stoppée par le polariseur (Fig.I.5 (b)). Dans ce cas, la cellule est bloquée (absence de lumière). Une fois que le champ électrique s'annule, la structure en hélice des molécules se reforme et la cellule reprendra son état passant [18].

Fig.I.5.Représentation et principe de fonctionnement d'une cellule à cristaux liquides dans un écran plat ou LCD [18]

Ce changement d'orientation des molécules induit une variation du plan de polarisation et donc une variation de la transparence de l'ensemble du dispositif. Cette variation de transparence est exploitée par un rétro-éclairage, par réflexion de la lumière incidente ou par projection. Nous distinguons trois types de modes d'éclairage adaptés à chaque contexte d'utilisation:

- Eclairage transmissif : C'est le système le plus classique car l'écran fonctionne avec aun rétro-éclairage utilisant des tubes fluorescent ou CCFL (Cold Cathod Fluorescent Seulement la luminosité et la consommation électrique de la source Lamp). lumineuse sont insuffisantes (images aux couleurs plus ternes et mauvaise reproduction de l'espace colorimétrique ou gamut). La durée de vie limitée des lampes influençant la durée de vie des écrans (2,4 fois plus qu'un écran cathodique avec 60 000 heures soit 33 ans avec l'écran allumé 5 heures par jour) [19].

- b-Éclairage réflectif : L'écran fonctionne avec la réflexion de la lumière incidente présentant une luminosité naturellement adaptée à l'éclairage ambiant d'où une réduction de consommation grâce au système de rétro-éclairage supprimé mais une illisibilité de l'écran est observée quand l'éclairage ambiant est faible [20].

Ce type d'éclairage est présent dans divers dispositifs (assistants numériques personnels ou PDA: Personal Digital Assistant, calculatrices, les baladeurs et les montres ...).

Éclairage transflectif: c'est la combinaison des deux systèmes précédents. c-Disponible sur de nombreux assistants personnels (PDA) et certains appareils photo.

Une nouvelle technique d'éclairage s'est développée depuis l'année 2007 qui remplace la lampe à décharge par un ensemble de diodes électroluminescentes blanches. Celles-ci permettent à l'écran à cristaux liquides de couvrir 114 % de son espace et offrent un réglage beaucoup plus stable de l'équilibre des couleurs ainsi qu'une très bonne uniformité d'éclairage [21].

#### III.2. Ecrans LCD et leurs technologies mises en œuvre :

Bien que l'on connaisse l'existence des cristaux liquides depuis le début du XX<sup>éme</sup> siècle, leur application aux afficheurs n'a fait son apparition qu'en 1968, suite à la découverte de l'effet de champ sur ces cristaux liquides. Une autre propriété intéressante est d'offrir une torsion ou une réorientation à l'axe des molécules d'un angle compris entre 90° et 220°. Cette torsion ou ce phénomène donne son nom au matériau d'où un écran plat à technologie TN-LCD ou Twist Nematic Liquid Crystal Display.

#### III.2.1. Ecrans LCD à nématique en hélice ou à matrice passive:

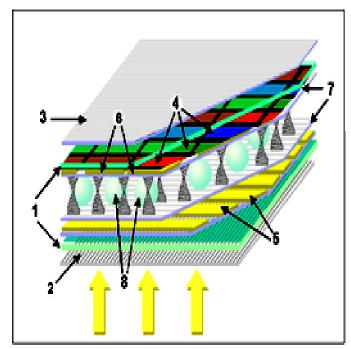

La technologie de base LCD à nématique en hélice ou TN (Twisted nematic) fût la plus répandue et la plus simple à réaliser, malgré des insuffisances dans le rendu des couleurs et du contraste ainsi qu'un fort traînage ou balayage. Elle a été améliorée par l'avènement des écrans DSTN (Dual scan twisted nematic) où une stabilité de l'image est remarquable (en procédant à sa formation par un double balayage). Malgré les multiples améliorations, ces technologies dites à « matrice passive » offrent un contraste limité à 50:1(une qualité moyenne des noirs en général). Des écrans à double couche ou DSTN (Double Super Twisted nematic) ont également été produits pour optimiser l'équilibre chromatique de la lumière produite. Ainsi, les écrans TN et DSTN sont transparents au repos [22].

Or, la commande ou l'adressage d'un pixel (minuscule point composant l'image d'un écran) est une étape difficile à réaliser dans une matrice. Cette dernière désigne l'ensemble des lignes et de colonnes que constituent les différents pixels d'un écran.

Le système à matrice passive ou TN-LCD fût le premier à être utilisé dans l'adressage de la matrice d'écran qui se fait par balayage (voir Fig.I.6). Chaque pixel est adressé par ligne et par colonne. Pour allumer un pixel de l'écran, on doit sélectionner la ligne et la colonne puis envoyer le signal de commande. L'affichage de l'image est obtenu par un balayage total de tous les pixels un par un. Ainsi, chaque pixel devra retenir son état de telle sorte que l'image reste affichée pendant un balayage complet. Ce système est beaucoup plus lent pour convenir au flux des images vidéo. Ainsi, pour augmenter la résolution de l'écran, il faudra utiliser une autre technique d'adressage. Les matrices passives sont utilisées pour les écrans de petite taille comme ceux des montres, des téléphones et des jeux électroniques portables...

- 1 : plaque de verre

- 2, 3 : polarisants verticalet horizontal

- **4** : filtre couleur RVB

- **5,6**: électrodes horizontales et verticales

- 7 : couches polymère d'alignement

Fig.I.6. Écran à cristaux liquides à nématique en hélice ou TN-LCD [22].

#### III.2.2. Ecrans LCD à matrice active ou AMLCD :

A l'origine du développement technologique basé sur des matrices passives, les écrans ont rapidement évolué vers une nouvelle génération de matrices dites actives. Pour ces matrices, l'idée est de commander chaque pixel par des dispositifs électroniques de commutation. Ces éléments connus sous leur acronyme anglais TFTs (Thin Film Transistors) pour désigner des transistors en couches minces. Or, on a souvent tendance à confondre LCD et TFTs; puisque ces derniers sont considérés couramment comme un type d'écran à technologie LCD.

#### i. Structure d'un écran à matrice active ou AMLCD :

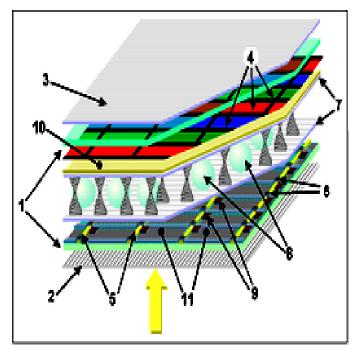

Un écran de type AMLCD (Active Matrix Liquid Crystal Display) est également composé de deux plaques de verre. La dalle inférieure contient la matrice de transistors TFT et celle supérieure un filtre coloré. Les cristaux liquides sont bien évidemment placés entre ces deux dalles comme il est illustré par la figure I.7. L'ensemble de l'écran est constitué de composants optiques (analyseurs, polariseurs, lampes d'éclairage et les cristaux liquides), de dispositifs électroniques d'adressage (TFT), et d'un système mécanique de maintien de l'ensemble [22].

**5**, **6** : lignes de commande horizontales et verticales.

7 : polymère d'alignement.

**9**: transistors.

10 : électrode frontale.

11 : électrodes élémentaires.

Fig.I.7. Structure d'un écran à cristaux liquides et à matrice active ou AMLCD [22]

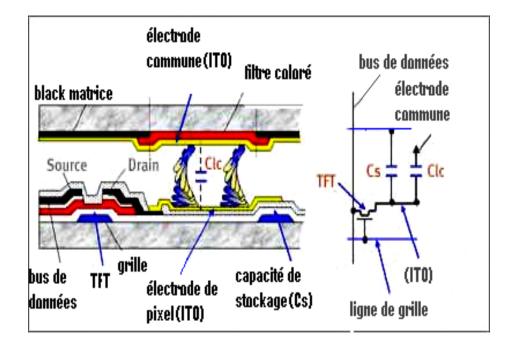

La plaque TFT est formée d'une matrice et de commutateurs. Les transistors en couche mince ou TFT sont déposés sur une dalle en verre (boro-silicate ou aluminosilicate). Un transistor par sous-pixel (trois par pixel en couleur) commande l'inclinaison du cristal liquide selon le champ électrique appliqué, ce qui permet de mieux contrôler le maintien de tension de chaque pixel d'où une nette amélioration du temps de réponse et de la stabilité de l'affichage.

Quant à la plaque supérieure, celle-ci est représentée par une électrode en ITO (Indium Tin Oxide) ou oxyde d'indium et d'étain (voir Fig.I.8) [23]. L'ITO est un métal transparent, malléable et rare, ressemblant chimiquement à l'aluminium et au gallium. On ne le trouve qu'en quantité infime dans les mines de zinc. De plus, il assure une bonne conductivité électrique sans altérer la transparence du verre. Sa récente utilisation massive, notamment dans les écrans plats LCD a fait augmenter considérablement son coût durant ces cinq dernières années [24].

Fig.I.8. Coupe schématique d'un écran à matrice active et à cristaux liquides ou AMLCD et son circuit électrique équivalent [24]

Dans la matrice active, la grille est reliée à la ligne tandis que la source et le drain sont respectivement connectés à la colonne et au pixel en oxyde d'indium et d'étain (ITO).

#### ii. Procédé de fabrication d'un écran AMLCD:

C'est un processus automatisé de fabrication des dalles à cristaux liquides réalisé dans un environnement contrôlé des salles blanches. Ce processus utilise deux technologies génériques :

- ➤ Une technologie de fabrication du type semi-conducteur qui est mise en œuvre pour la réalisation de la matrice active, du filtre en couleur et leur assemblage [25].

- ➤ Une technologie d'assemblage où les diverses opérations font appel à des composants optiques (analyseurs, polariseurs, lampes d'éclairage...), à des composants électroniques d'adressage (TFT) et à un système mécanique de maintien de l'ensemble du module (écran).

La fabrication de la matrice active nécessite une juxtaposition de couches minces. La technologie mise au point est standard et identique à celle des semi-conducteurs qui utilise un certain nombre d'étapes de dépôt et de gravure de couches minces déposées sur un substrat (verre).

L'étape de départ est la mise au point d'une dalle de verre de grande dimension (1,9 m à 2,2 m pour les futures générations) de chaque face du module. Le verre déposé est d'une faible épaisseur (inférieure au millimètre), ce qui lui permet de résister aux différents traitements chimiques et thermiques sans déformation (température supérieure à 600 °C). A cet effet, on utilise des verres à forte teneur en silice. La plaque avant reçoit successivement les pigments du masque coloré (colorants en solution solide dans la résine), une couche de protection, une couche d'ITO (électrode avant) puis une couche de polyimide (un radical amonium lié à deux carbonyles R-C=O puis à un atome d'azote). Celle-ci est légèrement rainurée par frottement avec un velour spécial. La plaque arrière suit un processus plus complexe : dépôts de plusieurs matériaux (silicium, métal pour connexion des électrodes, lignes de données pour condensateur), oxydation, photolithographie, puis dépôt des espaceurs et finalement un film en polyimide [26].

L'assemblage par collage doit être extrêmement précis (de l'ordre du micromètre) afin d'assurer une parfaite correspondance entre le masque coloré et les sous-pixels. L'ensemble est rempli avec la solution en cristal liquide. Ses spécifications font intervenir sa viscosité et sa mobilité (35 à 40 mm<sup>2</sup>/s à 20°C) qui faciliteront l'opération de remplissage de la cellule et le bon fonctionnement de l'écran.

La dernière opération est l'application d'un film polarisant (acétate de polymère) de chaque côté de l'assemblage [27].

Par conséquent, l'investissement nécessaire pour monter une chaîne de production d'écrans plats LCD est colossale devant une technologie de pointe. Cette dernière, utilisée par des équipements rénovés, contribue majoritairement à faire augmenter incessamment le coût de ces écrans.

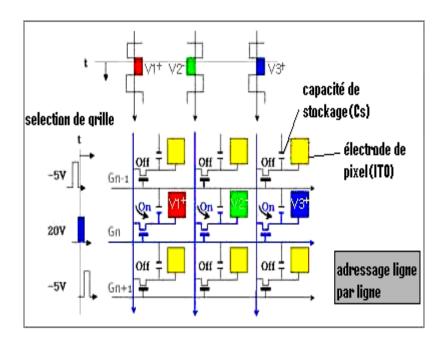

iii. Circuit d'adressage d'une matrice active à cristaux liquides (AMLCD) :

Le principe de l'adressage d'une matrice active direct est d'introduire au niveau de chaque pixel, en série avec la capacité du cristal liquide, un élément de contrôle (TFT).

Ce dernier permet de maintenir localement la tension nécessaire au basculement du cristal liquide lorsque la ligne correspondante est désactivée.

Cependant, l'adressage est réalisé lorsque une application d'une tension sur la première ligne sélectionnée où tous les transistors de celle-ci sont en état passant. Alors que toutes les colonnes sont mises sous diverses tensions en même temps. Ainsi, chaque pixel de la ligne est activé individuellement. Ensuite, on bloque tous les transistors (état off) de cette même ligne pendant l'adressage de la ligne suivante (Fig.I.8). Une capacité de stockage maintient ainsi la charge (joue le rôle de mémoire) jusqu'au prochain balayage de sorte que le contenu du pixel reste rafraîchi. L'image est donc affichée, après balayage de l'ensemble des lignes, avec une meilleure lisibilité et une bonne stabilité (meilleur contraste avec un temps de réponse rapide).

Notons qu'un pixel est composé par un arrangement de trois sous-pixels Correspondant aux trois couleurs primaires Rouge, Vert et Bleu (RVB) à 8 bits (256 niveaux de gris), ce qu'il lui permet d'afficher 1.67 millions de couleurs (2 <sup>8</sup>x 2 <sup>8</sup>x 2 <sup>8</sup>). Ce nombre peut augmenter mais ne présent aucun intérêt étant donné que l'oeil humain ne discerne autant de couleurs [28].

Fig.I.9. Adressage d'une matrice active à cristaux liquides AMLCD [28]

# III.2.3. Technologies et performances requises pour les transistors en couche mince:

Les technologies déclinées dans de nombreuses versions (IPS, S-IPS, MVA, PVA...) sont des évolutions de la technologie TN-TFT visant à corriger les défauts de cette dernière.

La technologie IPS (In-Plane Switching) développée en 1996 perfectionne la technologie TN-TFT en utilisant des cristaux liquides dont l'axe est parallèle au plan de l'écran. L'angle de vision est très large grâce au nombre de transistors qui a doublé avec une richesse en couleur remarquable, mais la transparence de l'image est légèrement diminuée [29].

Un perfectionnement a été introduit en 1998 par la technologie MVA (Multi-domaine Vertical Alignement), en intégrant plusieurs domaines de réfraction par cellule au niveau du cristal liquide. La qualité de l'image est fortement améliorée permettant ainsi d'augmenter le contraste utile et l'angle de vision. Le dernier développement en est le PVA (Patterned Vertical Alignement) qui atteint un contraste encore meilleure (1000:1 pour un écran 15 pouces).

Rappelons que, les écrans à matrice active ont été majoritairement fabriqués à base de TFTs de pixel. Ces derniers sont des transistors à effet de champ à grille isolée (ou MOSFET) dont les caractéristiques électriques sont exigées suivant qu'ils sont utilisés dans des circuits périphériques de commande ou dans la matrice active de l'écran.

a/ Circuits périphériques de commande : Ces circuits sont destinés à fonctionner à des fréquences élevées d'environ 10Mhz; dans ce cas la relation entre paramètres électriques du composant et la vitesse des circuits ne peut être négligée. En effet, une mobilité supérieure ou égale à 100 cm<sup>2</sup>/V.s, une tension de seuil inférieure ou égale à 5V, une pente sous le seuil inférieure ou égale à 1 V/décade et un rapport de courant  $I_{on}/I_{off} \approx 10^5$  sont nécessaire pour qu'un écran ait une bonne et forte résolution (applications dans le cas des projections vidéo à petit écran) [30].

b/ Eléments de la matrice active : Les TFTs employés dans l'adressage de pixels sont soumis certes à une condition sur la mobilité moins importante, mais ils doivent présenter

un rapport I<sub>ON</sub>/I<sub>OFF</sub> assez important d'où un courant de fuite I<sub>off</sub> le plus faible possible afin de minimiser la décharge de la capacité liée au cristal liquide à travers le transistor [31].

Par conséquent, le courant de fuite prend une importance capitale dans l'application des TFTs aux écrans plats. Son augmentation excessive dans les composants à semiconducteurs (particulièrement en polysilicium) trouve ses origines dans la structure du matériau utilisé.

Or, l'avènement spectaculaire des écrans plats LCD est associé à l'infrastructure et au développement technologique de fabrication des transistors en couche mince ou TFTs à base de silium polycristallin. Ces derniers ont ouvert la voie d'une nouvelle discipline dans la microélectronique, et sont actuellement un sujet de recherche privilégié.

#### III.2.4. Avantages des TFTs en poly-Si dans l'application AMLCD :

Toutes les technologies d'écrans plats (LCD, plasma, OLED...) évoluent rapidement pour répondre aux besoins des applications auxquelles elles sont dédiées. Sauf que l'évolution technologique des écrans AMLCD a répondu aux grands nombres d'exigences:

- Framps de réponse (2 à 16 ms) et un contraste (600 : 1 à 3000 : 1) qui sont nettement améliorés par rapport aux écrans passifs car les TFTs en poly-Si alimentent et maintiennent le courant appliqué aux pixels d'où augmentation de la diffusion de la lumière et orientation rapide du cristal liquide [32].

- Angle de vision plus large (178°) offert par l'amélioration et le développement de la technologie TN (technologies déclinées dans de nombreuses versions S-IPS, MVA, PVA...) [32,33].

- Faible consommation d'énergie qui est inférieure de 60% à celle des écrans CRT, et absence totale de dégagement de chaleur (0.5 à 3W pour un écran de 10 pouces).

- Taille et légèreté remarquables (quelques centimètres de profondeur ce qui explique l'aspect plat sur 40 pouces de diagonale) [33].

- © Robustesse et durée de vie importantes (50000 à 60000 heures soit environ 6 heures/jour un écran est allumé pendant 14 ans) [34].

- F Haute définition de l'écran (un écran couleur de 1024x768 pixels contient 2 3059 296 TFTs en poly-Si).

- F Absence de scintillement (rétro-éclairage fluorescent) améliore nettement la qualité de l'image [34].

En plus, les drivers TFTs en poly-Si qui sont intégrés directement sur le substrat en verre grâce à l'étendue mobilité du polysilicium (μ<sub>n</sub>=150 à 300 cm<sup>2</sup>/V.s en technologie TFT poly-Si avancée) par rapport au silicium amorphe (μ<sub>n</sub>=1 cm<sup>2</sup>/V.s) [18]. Cette intégration permet une augmentation du courant ON nécessaire au pilotage du pixel et donc une réduction du temps de charge plus rapide de sa capacité. Notons qu'un TFT est de dimension plus petite au sein du pixel, ce qui implique un meilleur taux de remplissage de celui-ci d'où un pixel plus lumineux offrant une meilleure lisibilité de l'image [18,35].

Malgré tous ces avantages, la technologie LCD a ses limites, particulièrement apparition de couleurs sombres qui ont un rendu moins performant (traces de lumière à l'écran parfois très gênant), même si cette technologie s'améliore de jour en jour [35].

# IV. Descriptions physique et électrique des transistors en couche mince (TFTs) à base de polysilicium:

Le TFT est un transistor à effet de champ composé d'une ou plusieurs couches semiconductrices non-monocristalline déposées sur un substrat isolant (voir Fig.I.10). De part le type du substrat, il est possible d'intégrer des transistors TFTs sur des surfaces beaucoup plus grandes contrairement aux transistors MOS, ce qui explique leur utilisation pour des applications en grande surface.

La technologie TFT sur substrat en verre est différente de celle à transistor MOS en monosilicium fabriqué en volume (ou transistor bulk). De plus, elle possède certains avantages par rapport à d'autres technologies telle que la technologie SOI (Silicon On Isulator) où le phénomène de latch-up est incontournable [36].

#### IV.1. Structure des transistors en couche mince (TFT en poly-Si):

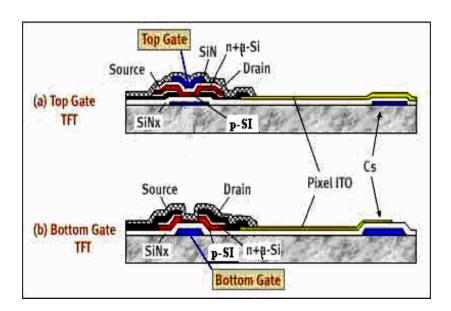

Les transistors en couche mince sont bidirectionnels (à structure symétrique) possédant trois terminaux source, drain et grille. Il existe deux configurations possibles de la juxtaposition des couches minces sur le substrat. La première est de type BISN (empilement Isolant Silicium Silicium), quant à la seconde configuration est du type BISI (empilement Isolant Silicium Isolant) [37]. Ces transistors unanimement utilisés par l'industrie d'écrans plats sont soit à gille en dessus (Top gate), soit dessous (Bottom gate) comme il est indiqué par la figure I.10. Chaque configuration présente ses avantages et ses inconvénients dont la différence reste minime sur le plan modélisation. Pour cela, nous ne ferons aucune distinction entre les deux représentations tout au long de notre étude.

Notons que le choix du substrat impose la température maximale utilisée lors du procédé technologique de fabrication du composant. On distingue, ainsi, deux types de transistors, ceux fabriqués à haute température couramment appelée HTPS (High Temperature Polysilicon) où le quartz est le substrat principalement utilisé. Bien qu'il présente des caractéristiques électriques peu dispersées, son coût excessivement élevé limite son utilisation qu'à des applications qui requièrent de petites surfaces [38].

Fig I.10. Structures et configurations possibles de transistors en couche mince destinés à l'adressage d'écran LCD [37]

- (a) A grille au dessus

- (b) A grille au dessous

Quant à la filière des transistors conçus à basse température ou LTPS (Low Temperature Polysilicon). Cette dernière est la plus employée en technologie des écrans plats à cristaux liquides (LCD), vue sa parfaite compatibilité et son faible coût. Les principaux substrats utilisés sont le verre (600 °C), l'acier (600 °C) ou le plastique (200 °C) (substrats souples) [39].

Or, pour la réalisation de la couche active, deux matériaux essentiels s'imposent: Le premier étant inorganique couramment employé (Silicium amorphe ou polysilicium dans notre cas), alors que le second est de type organique actuellement en voie de développement.

#### IV.1.1. Matériaux organiques :

Un semi-conducteur organique ou composé organique est sous la forme d'un cristal ou d'un polymère, présentant des propriétés similaires aux semi-conducteurs inorganiques (voir Fig.I.11). Ces propriétés sont la conduction par les électrons ou par les trous, ainsi que la présence d'une bande interdite. Ces matériaux ont donné naissance à l'électronique organique, ou électronique des plastiques. On dit " organique" par opposition aux semiconducteurs inorganiques, tel ''le silicium''.

Toutefois, dans les cristaux organiques formés par des molécules contenant des liens polymères, les électrons peuvent circuler librement, ce qui permet une conduction électrique comparable aux matériaux inorganiques.

De plus, comme les semi-conducteurs inorganiques, ils peuvent être dopés, c'est-àdire qu'on peut y introduire des électrons en excès (dopage de type N) ou des trous (dopage de type P). La technique préconisée est d'exposer le film de semi-conducteur organique à une vapeur d'un oxydant ou d'un réducteur, ce qui aura comme effet d'arracher ou d'ajouter des électrons [40].

Fig.I.11. Structure d'un composé organique [40]

Par conséquent, les semi-conducteurs organiques offrent certains avantages par rapport aux matériaux à semi-conducteurs :

- Légèreté : pratique pour la portabilité

- Flexibilité : moins fragiles que les semi-conducteurs inorganiques qui doivent être déposés sur des substrats plans et rigides.

- Facilité de fabrication et auto-assemblage : les semi-conducteurs sont généralement faciles et économiques à fabriquer en laboratoire. Le génie chimique peut mettre au point des molécules qui s'auto-assemblent. Ces méthodes de fabrication tranchent avec les processus onéreux et plus difficiles des technologies inorganiques (procédés et traitements à très hautes températures par exemple).

Les semi-conducteurs organiques sont actuellement utilisés dans le domaine de l'optoélectronique pour le développement des diodes électroluminescentes organiques (OLED: Organic Light Emitting Diode) [40]. Ces dernières sont les futurs dispositifs d'affichage concurrents des écrans LCD (Liquid Crystal Display) actuels. Seulement, leurs applications présentent quelques contraintes telles que :

- Temps de vie : le temps de vie des dispositifs d'affichage organique est plus court que celui des LCD. Cela est dû à la dégradation des molécules organiques qui donne un aspect à l'écran moins lumineux et sombre.

- Jetable : l'industrie voit dans les semi-conducteurs organiques, grâce à leur faible coût et à leur facilité de fabrication, une possibilité de réaliser des dispositifs électroniques jetables. Il y a lieu de se questionner sur l'aspect écologique d'une telle conception.

#### IV.1.2. Matériaux inorganiques :

Trois matériaux semi-conducteurs ont émergés et offrent plus ou moins des propriétés requises pour la réalisation de la couche active du canal des TFTs : le séléniure de cadmium (CdSe), le silcium amorphe (a-Si) et le silicium polycristalin ou polysilicium (poly-Si) [23]. Si les deux premiers matériaux ont présenté des avantages majeurs, leurs inconvénients sont indéniables dans l'adressage matriciel de l'écran [41].

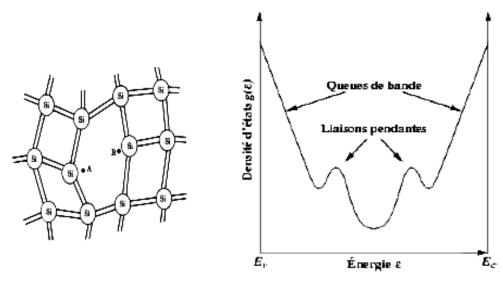

#### a/ Silicium amorphe:

L'arrangement des atomes dans le silicium amorphe est irrégulier présentant des distorsions apparentes dans le réseau comme il est montré par la figure I.12. Une distribution des états électroniques induite se traduit par l'apparition d'états localisés dans la bande interdite en haut de la bande de valence et en bas de la bande de conduction, que l'on appelle les queues de bande. Ces distorsions peuvent devenir suffisamment importantes pour empêcher une liaison de se former, et ainsi donner lieu à des liaisons pendantes.

Fig.I.12. Liaisons pendantes et représentation de la densité d'états énergétique dans la bande interdite du silicium amorphe [41].

Etant donné ses performances électroniques dégradées, le silicium amorphe fût rapidement abandonné dans la technologie de l'affichage au profit du silicium polycristallin dont les avantages sont indéniables. En effet, les dispositifs à base de silicium amorphe hydrogéné (a- Si :H) dont les propriétés de transport ( $\mu_n = 1 \text{ cm}^2/\text{V.s}$  et  $\mu_p = 10^{-3}~\text{cm}^2/\text{V.s})$  n'offrent pas de grande vitesse nécessaires à l'adressage d' un écran LCD ou à un signal vidéo.

#### b/ Silicium polycristallin ou polysilicium :

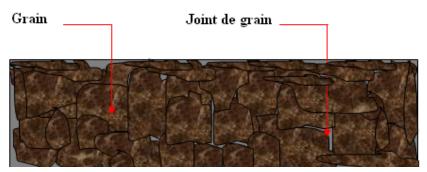

Le silicium polycristallin couramment appelé polysilicium est composé de grains monocristallins séparés les uns des autres par des régions désordonnées et riches en défauts cristallins appelées "joints de grains" (voir figureI.14).

Chacun de ces deux composants (grains et joints de grains) possède des caractéristiques propres : Le grain peut être défini par sa taille et par sa qualité cristalline, alors que les caractéristiques essentielles du joint de grain sont sa dimension, son épaisseur et plus particulièrement sa densité de défauts [42]. On peut donc distinguer plusieurs types de polysilicium qui seront classés selon deux critères :

- Texture et taille des grains.

- Densités de défauts intragranulaires et intergranulaires.

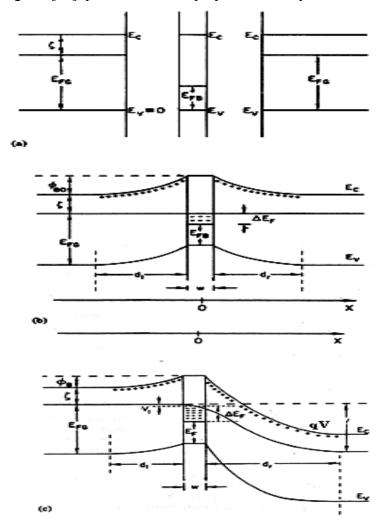

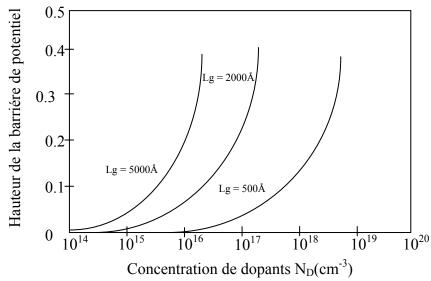

La structure du polysilicium dépend étroitement des conditions de dépôt, des méthodes de cristallisation et des post-traitements (recuit, hydrogénation...). Son mécanisme de conduction électrique est gouverné par le transport à travers le joint de grain où le phénomène de piégeage des porteurs joue un rôle prédominant. Ainsi, dans l'hypothèse d'un matériau polycristallin formé de grains de tailles identiques Lg (µm), de joints de grains d'épaisseur négligeable par rapport à lg avec une densité de pièges N<sub>T</sub> mono énergétique localisée par un niveau d'énergie E<sub>t</sub> dans la bande interdite, le problème peut être ramené au modèle de barrière de potentiel qui a été développé par KAMINS puis repris par LEVINSON [43]. Ce modèle tient compte des états pièges présents aux joints de grains qui deviennent électriquement actifs, et créent une barrière de potentiel. La mobilité effective des porteurs libres se trouve alors réduite dans la couche active (en polysilcium) qui constitue le canal du TFT (Voir Fig.I.13).

Ce phénomène de piégeage des porteurs joue un rôle prépondérant dans le mécanisme de conduction du polysilicium, qui se répercute directement sur les caractéristiques électriques du transistor en couche mince à base de polysilicium ou TFT en poly-Si.

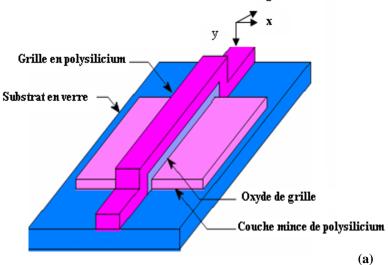

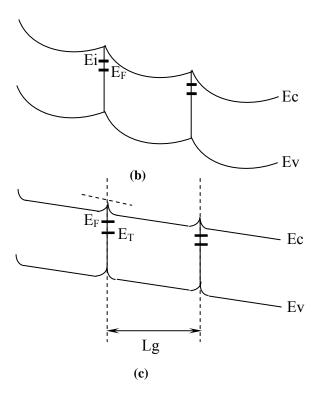

Fig.I.13. Structure d'un TFT à base de polysilicium [43]

- (a) Représentation de la structure du TFT à 3D

- (b) Distribution des bandes d'énergies dans le cas d'une déplétion complète des grains

- (c) Distribution des bandes d'énergie dans le cas d'une déplétion partielle des grains

Par ailleurs, l'élaboration du film de polysilicium est obtenue par décomposition du disilane Si<sub>2</sub>H<sub>6</sub> en phase vapeur à basse pression LPCVD (Low Pessure Chemical Vapor Deposition) et à faible température (T=480°C). Cette étape est suivie par une implantation ionique du bore à une dose de 5x10<sup>15</sup>cm<sup>-2</sup> dans le cas du film polysilicium de type P. Alors que la couche polycristalline de type N a été élaborée par procédé LPCVD à Td=450°C puis dopée in-situ au phosphore et recuit sous R.T.A à 1050 °C durant 30s.

L'observation du film polycristallin, par la technique de Microscopie Electronique à Balayage (MEB), nécessite une étape de préparation préliminaire. Cette dernière consiste à faire tremper le film obtenu pendant quelques secondes dans une solution SECCO qui vise à révéler les grains tout en attaquant les joints de grains qui sont des régions amorphes.

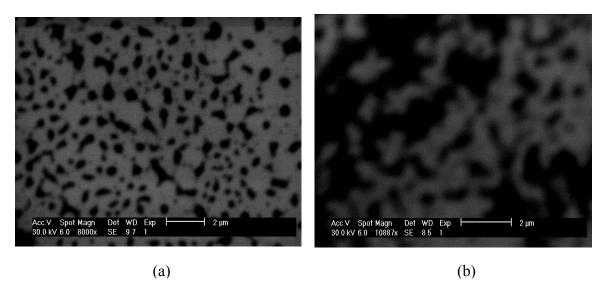

La figureI.14 représente une image MEB d'une couche de polysilicium implantée bore après recuit thermique à 850°C durant 15 minutes, où nous observons une structure typiquement polycristalline à gros grains dont la taille moyenne d'un grain est estimée à 1,5 µm d'environ (Fig.I.14 (a)). Quant à la Fig.I.14 (b) représente l'observation MEB d'un film de polysilicium dopé au phosphore (recuit sous R.T.A à 1050°C) à petits grains  $(0.3 \mu m.)$ .

Fig.I.14. Observation MEB d'un film de polysilicium élaboré par la technique L.P.C.V.D.

- (a) Film de polysilicium à gros grains, dopé bore après recuit thermique (850 °C, 15 mn).

- (b) Film de polysilcium à petit grains, dopé phosphore après recuit thermique (1050 °C, 30s)

L'intérêt du polysilicium est encore un domaine d'actualité, pour la fabrication des TFTs qui sont de nos jours établis comme faisant partie d'un développement technologique important. Ces derniers se focalisent sur les filières TFTs en poly-Si élaborés à basse température vu qu'elles sont parfaitement compatibles et adaptées à leurs contraintes (application en grande surface, faible coût, écrans souples ...).

Par conséquent, la technologie du silicium polycristallin à basse température, qui présente des caractéristiques électriques nettement meilleures (mobilité supérieure à 200 cm<sup>2</sup>/V.s), facilite l'intégration directe de tous les dispositifs TFTs sur un substrat en verre ou plastique. Ce qui permet d'éviter nombreux problèmes de leurs connexions vers l'extérieur, tout en assurant une meilleure fiabilité (bon fonctionnement électrique) [26].

Dans le cadre de cette thèse, nous n'étudierons que les TFTs en poly-Si élaborés à basse température ou TFTs LTPS (600 °c comparé au procédé technologique du monsilicium à 1000°C), en raison de leur rôle dans le progrès spectaculaire de la technologie

d'affichage en particulier. En plus, une couche polycristalline permet de graver des circuits plus performants d'un facteur 100 par rapport au silicium amorphe et, bien sûr, d'obtenir une plus grande finesse [44].

#### IV.2. Régimes de fonctionnement du TFT en poly-Si à basse température :

Le principe de fonctionnement du TFT en poly-Si est similaire à un transistor MOS monocristallin fabriqué en volume (transistor bulk). Il se base sur une conduction par effet de champ dans le canal (N ou P) qui se forme entre la source et le drain. Cette conduction est modulée par la polarisation de la tension de grille qui détermine le régime de fonctionnement du dispositif. Lorsqu' une tension de drain est appliquée, le courant entre la source et le drain circule. En effet, pour un TFT en poly-Si à canal n, une tension de grille positive ( $V_G \ge V_T$ : tension de seuil) provoque une accumulation d'électrons où un courant de diffusion s'établit (régime linéaire). Au fur et à mesure que cette tension augmente, le nombre de charges libres s'accroît jusqu'à saturation de tous les états pièges localisés dans la bande interdite (régime de saturation). On atteint alors le régime ON du transistor ( $V_G = V_{ON}$ ) [45].

Dans cette zone de fonctionnement, les caractéristiques électriques telles que concentration des porteurs et leur mobilité sont fortement liés à la structure du polysilicium (taille des grains, densité de pièges présente aux joints de grains).

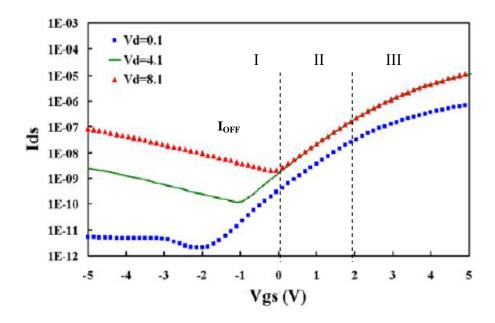

Selon les propriétés du film de polysilicum, les états d'interface et la tension de grille, trois régimes de conduction peuvent être identifiés (zones I, II et III) : un régime de blocage ou de fuite, début de l'accumulation ou régime de diffusion, et enfin le régime de conduction d'où un courant entre la source et le drain réparti comme suit :

- Régime de fuite (zone I): Le courant de fuite I<sub>OFF</sub> dans le polysilicium est élevé. Il augmente avec les tensions V<sub>ds</sub> et Vgs même après avoir atteint le minimum, le transistor est en état bloqué comme il est clairement montré par la figure I.14. Ce courant est l'une des limitations majeures des performances des TFTs.

- Régime linéaire (zone II) : Cet intervalle de fonctionnement correspond à un début d'accumulation des porteurs dans le canal où un courant de diffusion (I<sub>ON</sub>) s'établi. Notons que la concentration est moins élevée côté drain à cause du potentiel appliqué.

Régime de conduction ou saturation (zone III) : Au fur et à mesure que la tension de grille augmente, la majorité des porteurs induits par celle-ci contribuent au courant de conduction dans le canal [45].

Dans la suite de notre étude, le courant de fuite fera l'objet d'un examen plus détaillé vu l'importance qu'il revêt d'une manière générale dans les caractéristiques électriques des **TFTs**

Fig.I.15. Evolution du courant de drain I<sub>ds</sub> avec la tension de grille V<sub>gs</sub> d'un TFT en poly-Si à canal N de dimension 50µmx50µm [45]

# IV.3. Paramètres électriques des TFTs en poly-Si :

### IV.3.1. Courant de fuite:

Le courant de fuite I<sub>OFF</sub> est induit par la jonction inverse qui se crée entre le drain et le canal lorsque le TFT en poly-Si est à l'état bloqué. Notons que ce courant est indépendant de la tension de grille V<sub>gs</sub> tant que celle-ci est faible devant la tension de drain V<sub>ds</sub>. Dés que cette dernière augmente, le courant I<sub>OFF</sub> prend des valeurs élevées Plusieurs mécanismes de conduction ont été proposé afin d'élucider l'existence de ce courant et son augmentation avec la tension de grille appliquée [45,46] :

- A faible tension V<sub>ds</sub>, le courant I<sub>OFF</sub> est dominé par le mécanisme de générationrecombinaison dans la zone de déplétion de la jonction canal-drain (en polarisation inverse) où les centres de pièges à porteurs présents aux joints de grains agissent comme sites favorables [46].

- A forte tension V<sub>ds</sub>, de nombreux mécanismes ont été fourni afin de justifier l'augmentation du courant I<sub>OFF</sub> dont nous citons : émission par effet tunnel (bande à bande), émission thermique assistée par le champ électrique (Poole-Frenkel) où la génération assistée par le champ est un phénomène qui peut être à l'origine du courant de fuite dans le polysilicium

Autres que ces mécanismes, le courant de fuite et sa variation avec les tensions de grille et de drain peuvent être affectés par un effet de canal court si les dimensions du canal sont inférieures à 10 µm. Aussi, un phénomène de multiplication des porteurs par avalanche peut avoir lieu suite à un effet d'un champ électrique élevé dans la zone de charge d'espace au niveau du drain

#### IV.3.2. Tension de seuil :

Rappelons que la tension de seuil dans le transistor MOS est évaluée entre la source et le drain pour laquelle la zone d'inversion apparaît dans le composant. Or, la transition entre les régimes OFF à ON étant très rapide, les valeurs des tensions de seuil sont pratiquement faibles (inférieures à 1V).

Contrairement au transistor monocristallin, un TFT en poly-Si dont la commutation du régime OFF à ON se produit plus lentement, en raison de la structure granulaire de la couche active. Effectivement, les porteurs libres par la polarisation de la grille se font plus rapidement capturés par les états pièges présents aux joints de grains.

Ce qui induit à une concentration en porteurs libres de plus en plus réduite dans le canal d'où une conduction plus lente.

Dans ce cas, on défini la tension de seuil V<sub>T</sub> par le prolongement de la pente linéaire de la caractéristique  $I_{ds}(V_{gs})$  et l'axe  $V_{gs}$  qui a pour intersection la valeur ( $V_T+V_{ds}/2$ ) [47].

# IV.3.3. Pente sous le seuil :

La pente sous le seuil est un paramètre qui défini la vitesse de commutation du régime OFF à ON du transistor.

Elle dépend de la densité d'états des pièges dans la bande interdite du polysilicium. En effet, lorsque la tension V<sub>gs</sub> augmente, les états pièges continuent à se remplir, ralentissant la mise en conduction du transistor. La transition du mode OFF à ON étant beaucoup plus lente dans le TFT en poly-Si où la pente sous le seuil est estimée entre 0.1 à 1 V/décade comparée à celle du transistor en bulk (50 à 100 mV/décade) qui est 10 fois plus faible.

Par conséquent, ce paramètre doit être aussi faible que possible afin d'assurer un faible courant de fuite et une vitesse de commutation élevée [47].

On peut, ainsi, classer les pentes sous le seuil en fonction de la taille des cristaux du matériau silicium (Monsilicium, polysilicium et silicium amorphe).

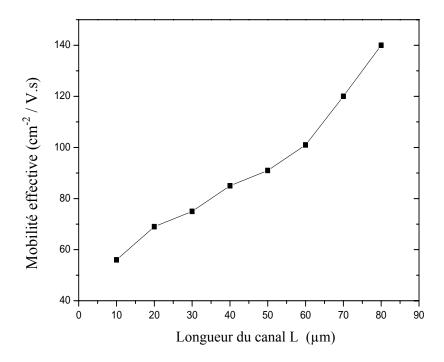

## IV.3.4. Mobilité des porteurs :

Rappelons que les performances des TFTs d'un écran LCD à très haute résolution, sont utilisés à la fois comme commutateur électronique pour l'élément d'image (pixel) et dans la réalisation d'un registre d'adressage (driver) pour l'intégration de l'électronique périphérique de commande. C'est la raison pour laquelle ces TFTs à couche active en polysilicium doivent avoir une mobilité suffisamment élevée pour envisager leur utilisation dans une telle application.

Dans le cadre de cette étude, nous nous intéressons qu'à la mobilité linéaire globale du composant TFT à grille au dessus, dite mobilité à effet de champ. Son extrapolation est obtenue à partir du tracé de la pente de la partie linéaire de la caractéristique  $I_{ds} = f(V_{gs})$ .

Toutefois, la mobilité dans un TFT est fortement liée à la structure du canal.

Elle est fortement diminuée, par la présence des joints de grains, d'un facteur 2 à 3 fois inférieur par rapport à la mobilité d'un transistor monocristallin. Ainsi, la mobilité est étroitement liée aux propriétés structurales du film de polysilcium, et aux différentes tensions appliquées [48].

# IV.3.5. Influence de la taille des grains sur les paramètres électriques du TFT poly-Si:

Dans l'optique de minimiser le temps de transition des porteurs en vue d'augmenter leur mobilité, tous les travaux de recherche s'accordent à montrer que les caractéristiques électriques du TFT à base du polysilicium dépendent étroitement de sa structure (taille des

grains du polysilicium) et de ses dimensions géométriques (longueur et largeur du canal). En effet, les paramètres électriques (I<sub>ON</sub>, V<sub>T</sub>, pente sous le seuil, mobilité...) sont nettement améliorés pour des tailles des grains supérieures à 1 µm ou une réduction de la longueur du canal inférieure à 10µm. Ce qui demeure très envisageable pour une application aux écrans plats à cristaux liquides [48,49].

Cependant, en réduisant la taille du composant, on diminue aussi bien le nombre des grains que celui des joints de grains présents dans la couche active. Ce qui a pour effet d'augmenter la mobilité et la pente sous le seuil, alors que le courant de fuite et la tension de seuil tendent vers des valeurs de plus en plus faibles.

# IV.4. Stabilité des paramètres électriques :

La stabilité des paramètres électriques d'un transistor influence directement sur les performances électriques de l'application désirée. Une variation de la tension de seuil affecte directement le courant I<sub>ON</sub> du transistor qui a pour effet de modifier la luminance de l'écran pour une même tension de commande V<sub>DATA</sub> appliquée à titre d'exemple.

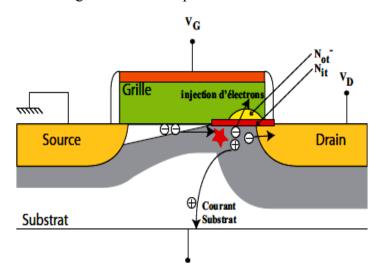

Un des principaux mécanismes de la dégradation, d'un ou de plusieurs de ces paramètres électriques, est l'injection d'électrons chauds de la source vers le canal sous l'effet d'un champ intense. L'accroissement du nombre d'électrons injectés qui devient de plus en plus cumulatif, conduit au phénomène d'avalanche. On observe, donc un phénomène qu'on appelle couramment effet kink caractérisant l'augmentation brutale du courant source-drain en fonction de la tension de drain décelé dans la caractéristique de sortie.

Dans un prochain chapitre, nous montrerons également que les états profonds et les queues de bandes contribuent d'une façon directe au bon fonctionnement du transistor (pente sous le seuil et caractéristique électrique au dessus du seuil).

# IV.5. Effet kink:

La réduction constante de la dimension des transistors est le moteur de la course à la performance électronique, notamment l'amélioration de la vitesse du fonctionnement du composant. Cette dernière est nettement améliorée par la diminution de la longueur du canal mais engendre quelques effets indésirables sur le comportement électrique du transistor.

#### IV.5.1. Phénomène d'impact par ionisation :

Dans la jonction canal-drain polarisée en inverse du TFT en poly-Si se crée un champ électrique d'autant plus important que la longueur du canal diminue. Les porteurs accélérés (porteurs chauds) par ce champ acquièrent suffisamment d'énergie cinétique pour créer un phénomène d'ionisation par impact. L'ionisation par impact ou par choc apparaît dans un matériau pour des champs intenses, ce qui permet à certains électrons de la bande de conduction d'acquérir une énergie suffisante, de telle sorte que leur interaction sur un atome du réseau cristallin contribue à la rupture d'une liaison de valence. L'accroissement du nombre d'électrons injectés de la source vers le drain provoque une augmentation du nombre de paires d'électrons-trous et un pincement remarquable du canal côté drain (voir Fig.I.16). Ceci, entraîne un abaissement de la barrière à la jonction source-drain encore plus prononcé, et de ce fait plus d'électrons injectés de la source vers le drain [50]. Le processus qui devient de plus en plus cumulatif donne naissance au phénomène d'avalanche. Ce phénomène est couramment appelé effet kink caractérisant une augmentation brutale de la caractéristique I<sub>ds</sub>(V<sub>ds</sub>). Généralement la dégradation des propriétés électriques observée dans les composants MOS [50] induit à :

- Une tension de seuil élevée, ce qui a pour conséquence une diminution du courant I<sub>ON</sub>.

- ➤ Une mobilité des porteurs libres du canal minimale

- Une variation significative de la pente sous le seuil.

Fig.I.16. Phénomène d'impact par ionisation dans un MOSFET à canal n [50]

# IV.5.2. Réduction de l'effet kink et technologie LDD :

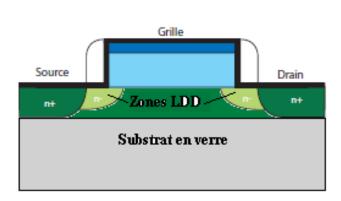

Dans le but de minimiser les effets nocifs de l'injection des porteurs énergétiques dans les composants MOS en général. Les concepteurs ont dû modifier leur structure conventionnelle (une seule diffusion pour la source et le drain), en dopant légèrement les zones de drain et de source qui sont directement en contact avec le canal comme il est indiqué par la figure I.17. Les zones de diffusion faiblement dopées dites LDD (Lightly Doped Drain) ont pour conséquence majeure la réduction du champ électrique latéral maximal [51].

Fig.I.17. Structure d'un TFT en poly-Si comprenant des zones faiblement dopées LDD (Lightly Doped Drain) [51]

# V. Technologies émergentes et concurrentes :

L'argument déterminant vers une technologie plus prometteuse apparaît aujourd'hui plus économique que technique. En effet, bien que la technologie semble encore disposer d'un réservoir d'amélioration pour la qualité de l'image d'un écran et de son coût. Elle n'adresse qu'un segment de marché particulier (taille plus large de 40" à 60"), alors que les écrans LCD tendent à se positionner sur l'ensemble des marchés y compris celui-ci.

Par ailleurs, les énormes investissements dont se montre capable l'industrie LCD et l'ampleur des moyens économiques qui lui donne un avantage certain sur l'écran à plasma.

De plus, même si ce dernier bénéficie d'un avantage important en angle de vue par rapport à LCD en vision directe, la technologie plasma se trouvait récemment désavantagée par une limitation en luminance et un coût du produit excessif. En fait, on assiste à une course de vitesse entre les investissements LCD nécessaires pour faire face à une demande qui couvre tous les formats et les dernières étapes d'évolution technologiques des écrans plats.

La technologie émergente qui suscite le plus d'intérêt tant au niveau de la l'industrialisation commercialisation que est la technologie diodes électroluminescentes organiques ou OLED incorporées dans la matrice à TFT en poly-Si.

# V.1. Technologie d'écrans plats à diodes électroluminescentes organiques (OLED):

La technologie OLED (Organic Light-Emitting Diode) est appelée à un développement rapide au cours des dix années à venir. Cette technique vise à remplacer les affichages à cristaux liquides LCD dont les avantages sont nombreux que nous citerons ultérieurement.

En effet, les premiers écrans OLED sont déjà en vente. Ces écrans sont très prometteurs, mais à l'heure actuelle, leur commercialisation n'est pas réaliste, en raison, d'une part, de leur prix trop élevé, et d'autre part, des limites actuelles de la technologie : écran très petit offrant une définition faible. Le plus grand écran OLED ne dépasse 27 pouces de diagonale, ce qui est nettement limité comparés aux écrans LCD (voir Fig.I.18) [52].

Fig.I.18. Modèles d'écrans OLED de taille variant de 11" à 27"[52]

#### V.1.1. Structure d'une OLED:

Les diodes électroluminescentes organiques sont réalisées à partir de polymères ou de molécules organiques qui ont des propriétés comparables aux semiconducteurs inorganiques (polysilicium, silicium monocristallin...). Cela signifie qu'on peut modéliser leur comportement électronique sous la forme d'une structure de bandes (bande de conduction et de valence séparées par un gap électronique).

- . Cependant, les propriétés qui confèrent un intérêt à l'utilisation de matériaux organiques pour la réalisation de diodes électroluminescentes sont :

- le caractère mou de ces matériaux permet s'ils sont déposés sur des substrats souples, de réaliser des composants flexibles.

- in coût de fabrication inférieur aux matériaux inorganiques pour des applications à faible durée de vie.

- ime consommation énergétique moindre.

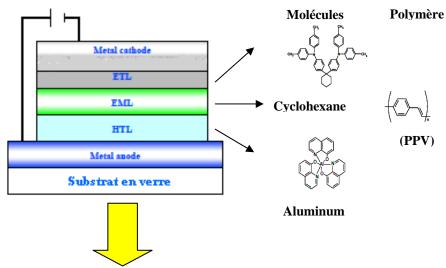

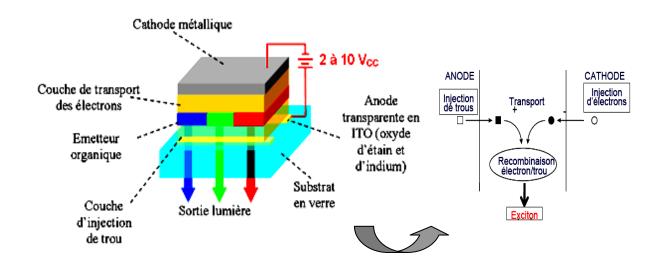

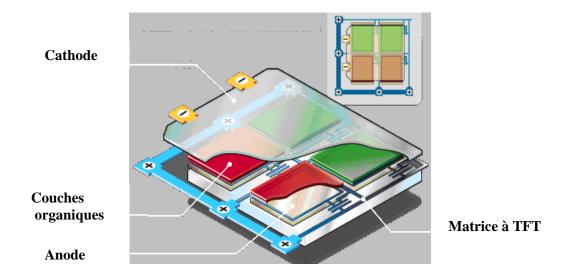

La structure géométrique typique d'une OLED est représentée par la figure.I.19 où les couches ETL (Electron Transport Layer) et HTL (Hole Transport Layer) sont dopées (mobilité faible d'un matériau organique par rapport au semiconducteur) et d'épaisseur très minces (quelques centaines d'angstroms) afin que le transport des électrons et des trous soit facilité [53].

Fig.I.19. Structure en couches d'une diode électroluminescente [53]